MT3620 のサポートの状態

重要

これは Azure Sphere (レガシ) のドキュメントです。 Azure Sphere (レガシ) は 2027 年 9 月 27 日に 再提供されておりユーザーは現時点で Azure Sphere (統合) に移行する必要があります。 TOC の上にある Version セレクターを使用して、Azure Sphere (統合) のドキュメントを表示します。

このドキュメントでは、MediaTek MT3620 に対する Azure Sphere サポートの現在の状態について説明します。 MediaTek MT3620 Web ページでダウンロードできるMT3620 製品概要を参照することもできます。 さらに、MediaTek は、MT3620 MCU を独自のハードウェアに統合するための詳細なガイドである MT3620 ハードウェア ユーザー ガイドを生成します。

重要

このドキュメントのコンテキストで、現在サポートされていないという文は、この機能のユーザー使用が現在制限されており、この制限が今後削除される可能性があることを意味します。 逆に、アクセスできないという文は、その機能をユーザーが使用できず、この制限が変更される可能性が低いことを意味します。

機能に関するご要望やフィードバックがある場合は、 Azure Sphere コミュニティ フォーラムへのご意見をお待ちしております。

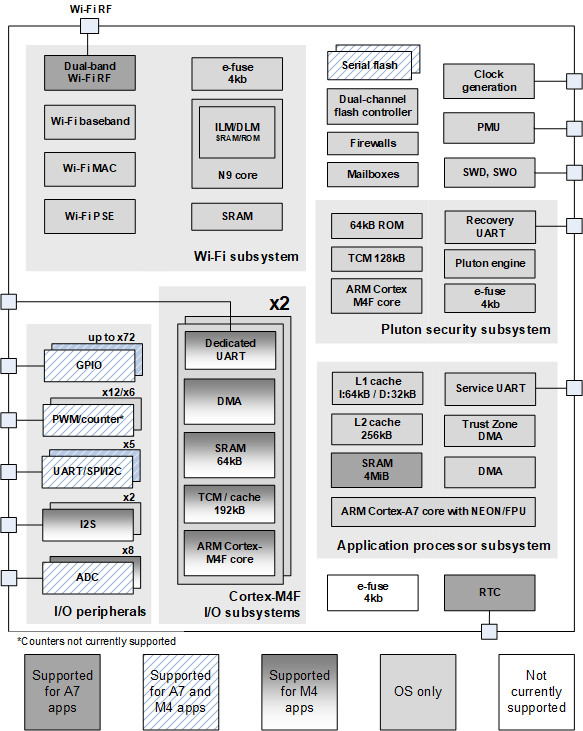

MT3620 ブロック図

ブロック図は、MT3620 コンポーネントごとに提供されるサポートを示しています。 図の後のセクションでは、これらのコンポーネントに関する追加の詳細を提供します。

I/O 周辺機器

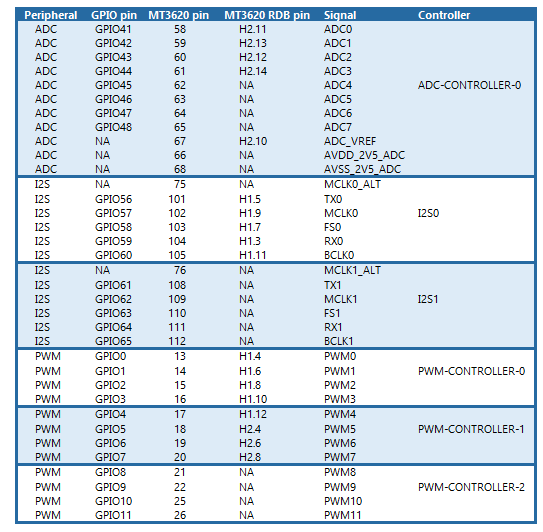

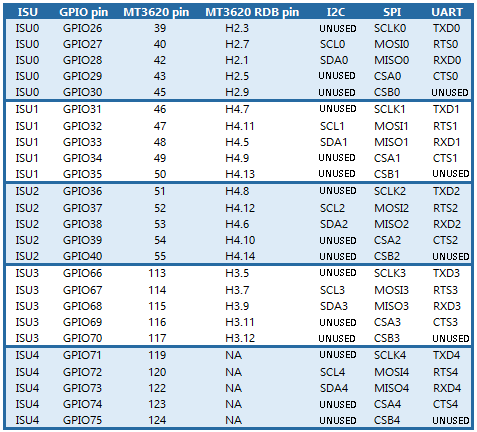

MT3620の設計には、計76個のプログラム可能なI/Oピンが含まれています。 次の 2 つの表に示すように、ほとんどのピンは汎用 I/O (GPIO) と他の機能の間で多重化されます。 記載されている GPIO ピンに加えて、GPIO12-23 は MT3620 ピン 27 から 38 でそれぞれ使用できます。

次の表を参照すると、"UNUSED" とマークされたピンは、関連付けられている ISU 周辺機器では使用されず、GPIO ピンとして使用するように構成できます。

Note

ISU 周辺機器がコアに割り当てられると、未使用のピンを含む 5 つの ISU ピンすべてが、そのコアでの使用に制限されます。

GPIO/PWM/カウンター

一部のピンは、GPIO、パルス幅変調 (PWM)、およびハードウェア カウンター間で多重化されています。

現在サポートされている GPIO 関数は、出力の高/低の設定と入力の読み取りです。 オープンドレイン/オープンソース駆動モードと駆動強度の制御もサポートされています。 外部割り込みは M4 コアではサポートされますが、A7 コアではサポートされません。

MT3620 には、PWM0 から PWM11 で識別される 12 個の PWM チャネルがあります。 これらは、それぞれ 4 つのチャネルから成る 3 つのグループに分類されます。 各グループは、PWM コントローラー (PWM-CONTROLLER-0、PWM-CONTROLLER-1、PWM-CONTROLLER-2) に関連付けられています。 PWM チャネルと GPIO ピン GPIO0 から GPIO11 は、MT3620 上の同じピンにマップされます。 アプリケーションで PWM コントローラーを使用する場合、そのコントローラーに関連付けられているすべてのピンは PWM 出力として使用するために割り当てられ、GPIO には使用できません。

PWM ハードウェアは、32 KHz、2 MHz (XTAL/13)、または 26 MHz (XTAL) の 3 つの固定クロック周波数のいずれかを使用するように構成できます。 リアルタイム (RT) コアでは、リアルタイム アプリケーション (RTApp) で、ベースとして使用するクロックを選択できます。 高レベル コア (A7) では、Linux ドライバーは常に 2 MHz クロックを使用します。 その結果、高レベル アプリケーションではデューティ サイクルと期間の制限が生じます。詳細なアプリケーションでの PWM の使用 で説明されているように。

シリアル インターフェイス (ISU) ブロック

MT3620 の設計には 5 個のシリアル インターフェイス ブロックがあり、そのそれぞれに 5 個のピンがあります (これらのブロックは "I2C、SPI、UART" を示す ISU とも呼ばれます)。これらのシリアル インターフェイス ブロックで、GPIO、ユニバーサル非同期送受信機 (UART)、相互集積回路 (I2C)、シリアル周辺機器インターフェイス (SPI) を多重化することができます。

UART は 1200、2400、4800、9600、19200、38400、57600、115200、230400、460800、500000、576000、921600、1000000、1152000、1500000、および 2000000 ボーでサポートされています。 32 バイトのハードウェア受信バッファーがあります。 次の UART 設定は、既定の設定として、8N1 で (8 データ ビット、1 ストップ ビット、およびパリティなし) でサポートされています。

- データ ビット: 5、6、7、8。

- ストップ ビット: 1 と 2。

- パリティ: 奇数、偶数、およびなし。

- フロー制御モード: RTS/CTS、XON/XOFF、フロー制御なし。

SPI トランザクションは最大 40 MHz までサポートされます。 各 ISU に最大 2 つの下位 SPI デバイスを接続できます。 ISU ポートを SPI マスター インターフェイスとして使用する場合、同じポートを I2C または UART インターフェイスとして使うことはできません。 1 回のバス トランザクションでの双方向の同時読み書き (全二重) SPI 操作はサポートされていません。 次の SPI 設定がサポートされています。

- 通信モード (クロック極性、クロック 位相): SPI モード 0 (CPOL = 0、CPHA = 0)、SPI モード 1 (CPOL = 0、CPHA = 1)、SPI モード 2 (CPOL = 1、CPHA = 0)、および SPI モード 3 (CPOL = 1、CPHA = 1)。

- ビット オーダー: 下位順に送信、上位順に送信。

- チップ セレクト極性: アクティブ高、アクティブ低。 アクティブ低が既定の設定です。

I2C では 7 ビット下位デバイス アドレスがサポートされています。 8 ビットまたは 10 ビットの I2C 下位アドレスはサポートされていません。 ISU ポートを I2C マスター インターフェイスとして使用する場合、同じポートを SPI または UART インターフェイスとして使うことはできません。 0 バイト I2C 読み取りはサポートされていません。 次の I2C 設定がサポートされています。

- 100 KHz、400 KHz、および 1 MHz バス速度。

- 操作のカスタム タイムアウト。

I2S

GPIO と I2S 間で 5 個のピンの 2 個のブロックが多重化されます。 i2S は、現在、M4 アプリケーションの場合にのみサポートされます。

ADC

MT3620 には、8 つの入力チャネルを持つ 12 ビット ADC が 1 つ含まれています。 GPIO と ADC の間に 8 つのピンのブロックが多重化されます。 ADC 入力チャネルと GPIO ピン GPIO41 から GPIO48 は、MT3260 上の同じピンにマップされます。 ただし、アプリケーションで ADC を使用する場合、8 つのピンはすべて ADC 入力として使用するために割り当てられ、GPIO には使用できません。

ARM Cortex-M4F サブシステム

MT3620 には 2 つの汎用 ARM Cortex-M4F サブシステムがあり、それぞれに専用の GPIO/UART ブロックがあります。

MT3620 では、既定のクロック レートである 26 MHz がサポートされています。 ただし、各 M4 コアは、HCLK_CK_CTRL レジスタを設定することによって、1 MHz から 200 MHz の間の任意のクロック レートで実行するように個別に構成できます。 次のコードは、クロック レートを 200 MHz に設定する 1 つの方法を示しています。

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Note

MT3620 での M4 コアのプログラミングの詳細については、MediaTek が公開している MT3620 のドキュメント 参照してください。 データシートに必要なすべての情報が記載されていない場合は、Avnet (Azure.Sphere@avnet.com) 宛てにメールして詳細なデータシートを依頼してください。

ARM Cortex-M4F サブシステムは、外部割り込みをサポートするようにプログラミングできます。 詳細については、「 リアルタイム対応アプリケーションで外部割り込みを使用する を参照してください。

アプリケーション プロセッサ サブシステム

ARM Cortex-A7 サブシステムは、Microsoft が提供する Linux ベースのカーネル、サービス、およびライブラリと共にカスタマー アプリケーションを実行します。

サービス UART は、A7 サブシステムのシステム機能専用です。 カスタマー アプリケーションには使用できません。

デバイス固有の情報を格納するための 1 回限りのプログラミング可能な e-fuse ブロックは、カスタマー アプリケーションでは使用できません。

Wi-Fi サブシステム

現在、Wi-Fi サブシステムは、2.4 GHz と 5 GHz の両方で IEEE 802.11b/g/n に準拠しています。

現在、Azure Sphere では WPA2、EAP-TLS、Open (パスワードなし) 認証のみがサポートされています。

無線周波数のテストと校正については、「RF test tools」(RF テスト ツール) を参照してください。

電源管理

MT3620 には、電力消費量を制御する Power Down および Power Profile 機能が含まれています。 詳細については、「 Power Down に関する考慮事項 および Power Profile に関する考慮事項 を参照してください。

クロックと電源

メイン水晶発振器は現在わずか 26 MHz です。 26 MHz 以外の水晶発信器の周波数は現在ソフトウェアではサポートされていません。

電圧低下の検出

電圧低下の検出は現在サポートされていません。

ハードウェア ウォッチドッグ タイマー

MTK3620には、いくつかのウォッチドッグ タイマーが含まれています。

- Pluton セキュリティ ドメインで使用するために専用の 1 つのウォッチドッグ タイマー。 このウォッチドッグ タイマーは、アプリケーションでは使用できません。

- アプリケーション プロセッサで使用できる 1 つのウォッチドッグ タイマー。 Azure Sphere OS では、システム サービスにこのウォッチドッグ タイマーが使用されます。 このウォッチドッグ タイマーは、アプリケーションでは使用できません。

- 各リアルタイム コアのウォッチドッグ タイマー。 これらのウォッチドッグ タイマーは、リアルタイム アプリケーションで使用できます。

詳細については、「 RTApp でウォッチドッグ タイマーを使用する を参照してください。

SWD、SWO

シリアル回線デバッグ (SWD、ピン 98 から 99) は M4 アプリケーションでのみサポートされます。 シリアルワイヤ出力 (SWO、ピン 100) は現在サポートされていません。 A7 アプリケーションのデバッグは、Microsoft で提供される gdb ベースのメカニズムによってサポートされています。

RAM とフラッシュ

MT3620 には、各 I/O サブシステムに 256 KiB、A7 アプリケーション サブシステムに 4 MB を含む約 5 MB の RAM がダイ上に搭載されています。

16 MB の SPI フラッシュ メモリが搭載された MT3620 を注文できます。

アプリケーションで使用可能な RAM およびフラッシュについては、「アプリケーションで使用可能なメモリ」を参照してください。

製造テストのサポート

カスタム製造テスト アプリケーションとファクトリ プロセスの統合をサポートするドキュメントとユーティリティはまだリリースされていません。

ピン出力

| ピン番号 | ピン名 | 主な関数 | Type | 説明 | コメント |

|---|---|---|---|---|---|

| 1 | GND | P | 接地 | ||

| 2 | AVDD_3V3_WF_A_PA | PI | 5 GHz Wi-Fi パワー アンプ用 3.3 V パワー レール | ||

| 3 | AVDD_3V3_WF_A_PA | PI | 5 GHz Wi-Fi パワー アンプ用 3.3 V パワー レール | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Wi-Fi 送受信用 1.6 V パワー レール | ||

| 7 | AVDD_1V6_WF_AFE | PI | Wi-Fi アナログ フロント エンド用 1.6 V パワー レール | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | メイン水晶発振器用 1.6 V パワー レール | ||

| 10 | MAIN_XIN | AI | メイン水晶発振器の入力 | ||

| 11 | WF_ANTSEL0 | 推奨 | 外部 DPDT スイッチ用の Wi-Fi アンテナ選択 | ||

| 12 | WF_ANTSEL1 | 推奨 | 外部 DPDT スイッチ用の Wi-Fi アンテナ選択 | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 23 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 24 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | PWM 出力で多重化された割り込み可能 GPIO | |

| 27 | GPIO12 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 28 | GPIO13 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 29 | GPIO14 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 30 | GPIO15 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 31 | GPIO16 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 32 | GPIO17 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 33 | GPIO18 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 34 | GPIO19 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 35 | GPIO20 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 36 | GPIO21 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 37 | GPIO22 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 38 | GPIO23 | DIO | 割り込み可能 GPIO | 割り込みは現在はサポートされていません | |

| 39 | GPIO26 | GPIO26/SCLK0/TXD0 | DIO | ISU 0 関数で多重化された GPIO | |

| 40 | GPIO27 | GPIO27/MOSI0/RTS0/SCL0 | DIO | ISU 0 関数で多重化された GPIO | |

| 41 | GND | P | 接地 | ||

| 42 | GPIO28 | GPIO28/MISO0/RXD0/SDA0 | DIO | ISU 0 関数で多重化された GPIO | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | ISU 0 関数で多重化された GPIO | |

| 44 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | ISU 0 関数で多重化された GPIO | |

| 46 | GPIO31 | GPIO31/SCLK1/TXD1 | DIO | ISU 1 関数で多重化された GPIO | |

| 47 | GPIO32 | GPIO32/MOSI1/RTS1/SCL1 | DIO | ISU 1 関数で多重化された GPIO | |

| 48 | GPIO33 | GPIO33/MISO1/RXD1/SDA1 | DIO | ISU 1 関数で多重化された GPIO | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | ISU 1 関数で多重化された GPIO | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | ISU 1 関数で多重化された GPIO | |

| 51 | GPIO36 | GPIO36/SCLK2/TXD2 | DIO | ISU 2 関数で多重化された GPIO | |

| 52 | GPIO37 | GPIO37/MOSI2/RTS2/SCL2 | DIO | ISU 2 関数で多重化された GPIO | |

| 53 | GPIO38 | GPIO38/MISO2/RXD2/SDA2 | DIO | ISU 2 関数で多重化された GPIO | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | ISU 2 関数で多重化された GPIO | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | ISU 2 関数で多重化された GPIO | |

| 56 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 57 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | ADC 入力で多重化された GPIO | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | ADC 入力で多重化された GPIO | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | ADC 入力で多重化された GPIO | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | ADC 入力で多重化された GPIO | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | ADC 入力で多重化された GPIO | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | ADC 入力で多重化された GPIO | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | ADC 入力で多重化された GPIO | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | ADC 入力で多重化された GPIO | |

| 66 | AVDD_2V5_ADC | PI | ADC 用 2.5 V パワー レール | ||

| 67 | VREF_ADC | AI | ADC 用参照電圧 | ||

| 68 | AVSS_2V5_ADC | P | ADC 用の接地 | ||

| 69 | EXT_PMU_EN | 推奨 | 外部電源対応の出力 | ||

| 70 | WAKEUP | DI | 最も深いスリープ モードからの外部ウェイクアップ | 現在、サポートされていません | |

| 71 | AVDD_3V3_RTC | PI | リアルタイム クロック用 3.3 V パワー レール | ||

| 72 | RTC_XIN | AI | リアルタイム クロック水晶発振器の入力 | ||

| 73 | RTC_XOUT | AO | リアルタイム クロック水晶発振器の出力 | ||

| 74 | AVDD_3V3_XPPLL | PI | 内部フェーズロック ループ用 3.3 V パワー レール | ||

| 75 | I2S_MCLK0_ALT | AO | MCLK0 の代替アナログ | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 | |

| 76 | I2S_MCLK1_ALT | AO | MCLK1 の代替アナログ | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 | |

| 77 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 78 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 79 | VOUT_2V5 | PO | 内部 2.5 V LDO からの出力 | ||

| 80 | AVDD_3V3 | PI | 3.3 V パワー レール | ||

| 81 | PMU_EN | DI | 内部 PMU のオーバーライド | ||

| 82 | RESERVED | ||||

| 83 | GND | P | 接地 | ||

| 84 | SENSE_1V15 | AI | 1.15 V 電源装置を安定させるセンス入力 | ||

| 85 | VOUT_1V15 | PO | 内部 1.15 V LDO からの出力 | ||

| 86 | AVDD_1V6_CLDO | PI | 内部 1.15 V コア LDO の 1.6 V パワー レール | ||

| 87 | PMU_CAP | A | PMU の安定性を維持するには、このピンと AVDD_3V3_BUCK 間にコンデンサーを接続してください | ||

| 88 | AVDD_3V3_BUCK | PI | 1.6 V 降圧 DC-DC コンバーター用 3.3 V パワー レール | ||

| 89 | AVDD_3V3_BUCK | PI | 1.6 V 降圧 DC-DC コンバーター用 3.3 V パワー レール | ||

| 90 | VOUT_1V6 | PO | 内部 1.6 V バック コンバーターからの出力 | ||

| 91 | VOUT_1V6 | PO | 内部 1.6 V バック コンバーターからの出力 | ||

| 92 | AVSS_3V3_BUCK | P | 内部 1.6 V バック コンバーターの接地 | ||

| 93 | AVSS_3V3_BUCK | P | 内部 1.6 V バック コンバーターの接地 | ||

| 94 | DEBUG_RXD | DI | Azure Sphere デバッグ用に予約済み | ||

| 95 | DEBUG_TXD | 推奨 | Azure Sphere デバッグ用に予約済み | ||

| 96 | DEBUG_RTS | 推奨 | Azure Sphere デバッグ用に予約済み | ||

| 97 | DEBUG_CTS | DI | Azure Sphere デバッグ用に予約済み | ||

| 98 | SWD_DIO | DIO | Cortex-M4F デバッグ用 ARM SWD | ||

| 99 | SWD_CLK | DI | Cortex-M4F デバッグ用 ARM SWD | ||

| 100 | SWO | 推奨 | Cortex-M4F デバッグ用 ARM SWO | 現在、サポートされていません | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | I2S 0 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 102 | GPIO57 | GPIO57/MCLK0 | DIO | I2S 0 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 103 | GPIO58 | GPIO58/FS0 | DIO | I2S 0 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 104 | GPIO59 | GPIO59/RX0 | DIO | I2S 0 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 105 | GPIO60 | GPIO60/BCLK0 | DIO | I2S 0 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 106 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 107 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | I2S 1 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 109 | GPIO62 | GPIO62/MCLK1 | DIO | I2S 1 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 110 | GPIO63 | GPIO63/FS1 | DIO | I2S 1 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 111 | GPIO64 | GPIO64/RX1 | DIO | I2S 1 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 112 | GPIO65 | GPIO65/BCLK1 | DIO | I2S 1 で多重化された GPIO | i2S は、現在、M4 アプリケーションの場合にのみサポートされます。 |

| 113 | GPIO66 | GPIO66/SCLK3/TXD3 | DIO | ISU 3 関数で多重化された GPIO | |

| 114 | GPIO67 | GPIO67/MOSI3/RTS3/SCL3 | DIO | ISU 3 関数で多重化された GPIO | |

| 115 | GPIO68 | GPIO68/MISO3/RXD3/SDA3 | DIO | ISU 3 関数で多重化された GPIO | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | ISU 3 関数で多重化された GPIO | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | ISU 3 関数で多重化された GPIO | 現在は GPIO のみがサポートされています |

| 118 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 119 | GPIO71 | GPIO71/SCLK4/TXD4 | DIO | ISU 4 関数で多重化された GPIO | |

| 120 | GPIO72 | GPIO72/MOSI4/RTS4/SCL4 | DIO | ISU 4 関数で多重化された GPIO | |

| 121 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 122 | GPIO73 | GPIO73/MISO4/RXD4/SDA4 | DIO | ISU 4 関数で多重化された GPIO | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | ISU 4 関数で多重化された GPIO | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | ISU 4 関数で多重化された GPIO | |

| 125 | SYSRST_N | DI | システムのリセット、アクティブ低 | ||

| 126 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 127 | SERVICE_TXD | 推奨 | Azure Sphere サービス ポート | カスタマー アプリケーションには使用できません | |

| 128 | SERVICE_RTS | 推奨 | Azure Sphere サービス ポート | カスタマー アプリケーションには使用できません | |

| 129 | SERVICE_RXD | DI | Azure Sphere サービス ポート | カスタマー アプリケーションには使用できません | |

| 130 | SERVICE_CTS | DI | Azure Sphere サービス ポート | カスタマー アプリケーションには使用できません | |

| 131 | RESERVED | ||||

| 132 | DVDD_1V15 | PI | 1.15 V パワー レール | ||

| 133 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 134 | RECOVERY_RXD | DI | Azure Sphere 復旧ポート | カスタマー アプリケーションには使用できません | |

| 135 | RECOVERY_TXD | 推奨 | Azure Sphere 復旧ポート | カスタマー アプリケーションには使用できません | |

| 136 | RECOVERY_RTS | 推奨 | Azure Sphere 復旧ポート | カスタマー アプリケーションには使用できません | |

| 137 | RECOVERY_CTS | DI | Azure Sphere 復旧ポート | カスタマー アプリケーションには使用できません | |

| 138 | IO0_GPIO85 | IO0_GPIO85/IO0_RXD | DI | I/O M4 0 用 UART で多重化された専用 GPIO | |

| 139 | IO0_GPIO86 | IO0_GPIO86/IO0_TXD | 推奨 | I/O M4 0 用 UART で多重化された専用 GPIO | |

| 140 | IO0_GPIO87 | IO0_GPIO87/IO0_RTS | 推奨 | I/O M4 0 用 UART で多重化された専用 GPIO | |

| 141 | IO0_GPIO88 | IO0_GPIO88/IO0_CTS | DI | I/O M4 0 用 UART で多重化された専用 GPIO | |

| 142 | IO1_GPIO89 | IO1_GPIO89/IO1_RXD | DI | I/O M4 1 用 UART で多重化された専用 GPIO | |

| 143 | IO1_GPIO90 | IO1_GPIO90/IO1_TXD | 推奨 | I/O M4 1 用 UART で多重化された専用 GPIO | |

| 144 | DVDD_3V3 | PI | 3.3 V パワー レール | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/IO1_RTS | 推奨 | I/O M4 1 用 UART で多重化された専用 GPIO | |

| 146 | IO1_GPIO92 | IO1_GPIO92/IO1_CTS | DI | I/O M4 1 用 UART で多重化された専用 GPIO | |

| 147 | RESERVED | ||||

| 148 | TEST | DI | 通常の操作では低に引き下げる必要があります | ||

| 149 | WF_G_RF_AUXIN | RF | 2.4 GHz Wi-Fi 受信ダイバーシティ ポート | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | 2.4 GHz Wi-Fi パワー アンプ用 3.3 V パワー レール | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | 2.4 GHz Wi-Fi アンテナ ポート (差分) | ||

| 154 | WF_G_RF_ION | RF | 2.4 GHz Wi-Fi アンテナ ポート (差分) | ||

| 155 | WF_G_RF_IOP | RF | 2.4 GHz Wi-Fi アンテナ ポート (差分) | ||

| 156 | WF_G_RF_IOP | RF | 2.4 GHz Wi-Fi アンテナ ポート (差分) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | 2.4 GHz Wi-Fi パワー トランスミット用 3.3 V パワー レール | ||

| 159 | WF_A_RF_AUXIN | RF | 5 GHz Wi-Fi 受信ダイバーシティ ポート | ||

| 160 | AVDD_3V3_WF_A_TX | PI | 5 GHz Wi-Fi パワー トランスミット用 3.3 V パワー レール | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | 5 GHz Wi-Fi アンテナ ポート (不平衡) | ||

| 163 | WF_A_RFIO | RF | 5 GHz Wi-Fi アンテナ ポート (不平衡) | ||

| 164 | GND | P | 接地 | ||

| 165 | EPAD | P | 接地 |