WavePci 裝置的硬體需求

選擇新硬體設計的功能時,廠商應遵循下列一般原則:

廠商應該根據每個功能對效能的影響來評估每個功能的成本,而不是直接將所有處理移至硬體。

在考慮硬體功能的潛在價值時,廠商應該根據整體對系統的影響來評估該功能,而不是將焦點縮小至特定子系統,例如音訊。

藉由在硬體中謹慎地選取哪些功能來加速,廠商可以減輕 CPU 工作負載並改善記憶體使用量,藉此讓系統的資源可供其他工作使用。

在過去,並非所有音訊硬體設計都成功遵循這些原則。

播放音訊內容或混合多個串流時,某些 WDM 音訊驅動程式不需要耗用大量的 CPU 時間和匯流排頻寬。 這類缺點通常是有瑕疵的硬體設計和沒有效率的驅動程式實作的結果。 硬體設計缺陷也可以防止音訊驅動程式處理特定波浪格式,或需要軟體介入的因應措施。

WaveCyclic 裝置型號的目的是要容納舊版音訊裝置的硬體限制。 新的硬體設計應該與 WavePci 完全相容。

可執行真實散佈/收集 DMA 的 WavePci 裝置,不需要 CPU 花費時間在緩衝區之間複製音訊資料。 不同于 WaveCyclic,WavePci 不需要進行資料複製,使其成為多串流或硬體加速音訊裝置慣用的迷你埠驅動程式。 設計良好的 WavePci 裝置幾乎不需要 CPU 資源,因此可以將大量音訊串流傳送 (至 64 或更多) ,以便進行 3D 處理和混合。

WavePci 裝置需要支援散佈/收集 DMA 傳輸的匯流排主機 DMA 控制器。 硬體設計不應該對 DMA 控制器可以處理的資料傳輸類型設定任意限制。 WavePci 裝置應符合下列需求:

裝置必須是匯流排主機。

它應該能夠自發存取系統記憶體,而不需從作業系統介入,而不需使用系統 DMA 資源。

裝置必須能夠處理任意長度的資料傳輸。

它應該處理 (看到 IPortWavePciStream::GetMapping) 大於記憶體頁面的對應。 例如,傳輸限制為 4 KB 的裝置不符合 WavePci 的完整需求。 在支援 Microsoft Windows 的 64 位 CPU 上,頁面大小為 8 KB,因此某些對應的大小可能會大於 4 KB。 根據實體記憶體片段,在單一對應中超過 32 KB 的資料傳輸理論上是可行的。 另一個極端是一個位元組的對應大小。

裝置應該處理系統記憶體中任何位置的資料傳輸。

跨越 32 KB 或較大兩個界限的資料傳輸很可能很可能。 電腦現在可以包含超過 4 GB 的 RAM,在這些系統中,在 64 位 CPU 或 x86 實體位址擴充功能 () 的情況下,對應可以位於實體記憶體中的 4 GB 以上。 為了達到這些機器的最佳效能,廠商應該建立支援 64 位定址的裝置。 否則,需要軟體中的資料複製。 在 RAM 超過 16 MB 的系統上,具有 24 位位址的裝置過去需要資料複製。 如果裝置無法從實體記憶體中的任何位置讀取或寫入,則應該使用 WaveCyclic,而不是 WavePci。 驅動程式可以在裝置啟動時做出此決策, (在有機會 判斷其位址觸達是否足以存取系統記憶體匯流排的完整位址範圍之後,看到IRP_MN_START_DEVICE) 。

裝置應該使用任意對齊方式處理資料傳輸。

對應可以在記憶體中的任意位元組界限開始和結束。 音訊資料的框架可以在對應之間分割,其中第一個對應結尾的前幾個通道範例,以及第二個對應中其餘通道的樣本。 如需範例,請參閱 Wave Filters。 對於某些範例大小,即使範例容器可以在對應之間分割。 如果裝置要求傳輸必須位於快取線界限上,或裝置要求傳輸嚴格對齊音訊畫面界限 (,例如,假設傳輸大小平均分成四個,在立體 16 位大小) 中,此裝置就不足以滿足完整的 WavePci 合規性。 請注意,不合規的硬體片段可以藉由限制驅動程式 (公開的資料範圍或格式來公開為 WavePci 裝置,例如,只有特定位深度或只有特定通道組態) 。

關於上述清單中的最後一點,WavePci 裝置的散佈/收集 DMA 引擎應該處理跨越記憶體頁面界限的緩衝區。 例如,48-kHz 的緩衝區包含 16 位 PCM 音訊樣本的 10 毫秒,5.1 通道波串流的大小如下:

(6 個範例/畫面) * (2 個位元組/樣本) * (48K 框架/秒) * (10 毫秒) = 5760 個位元組

這會超過記憶體頁面大小 (4096 個位元組) ,這表示緩衝區包含一或兩個頁面界限,視其位置在記憶體中的方式而定。 緩衝區包含音訊資料框架 (480 個) 整數,但其中一或兩個畫面格可能會跨越頁面界限。

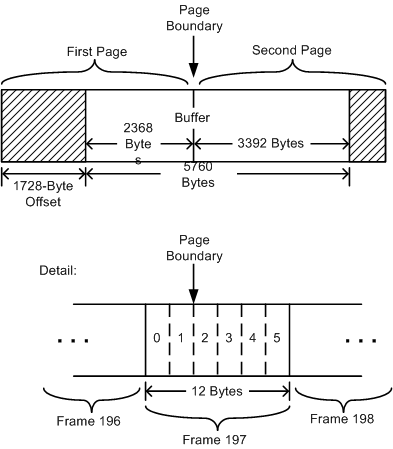

基於這個理由,WavePci 裝置的散佈/收集 DMA 硬體應該設計成處理音訊畫面 (,例如下圖中的框架 197) 分割在記憶體中的兩個實體非連續分頁之間。

在上圖頂端是 5760 位元組緩衝區,會在兩個頁面之間跨越界限。 在此範例中,緩衝區會從第一頁的開頭開始 1728 位元組位移開始,這會將緩衝區的開頭對齊記憶體中的 64 位元組界限。 假設每個音訊畫面佔用 12 個位元組,並包含六個通道。 第一頁包含所有畫面 0 到 196,但只包含框架 197 的前四個位元組。

圖底部是音訊框架 197 的詳細檢視,其中顯示只有通道 0 和 1 的範例落在第一頁。 第二頁包含通道 2 到 5 的範例。

雖然這兩個頁面出現在圖形頂端的旁邊,但事實上,它們只會在核心虛擬記憶體中連續。 因為包含緩衝區的頁面在實體記憶體中不連續,所以散佈/收集 DMA 控制器會使用實體位址,必須將緩衝區的兩個部分指定為其傳輸佇列中的兩個個別專案。 WavePci 埠驅動程式會自動將緩衝區分割成頁面界限上的兩個不同的實體對應。

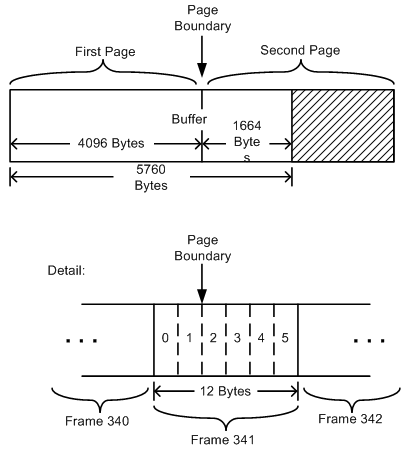

即使上述範例已變更為將緩衝區與第一頁的開頭對齊,分割框架問題也不會消失。 下圖示范這個點。 在此情況下,畫面 341 會在頁面界限上分割,其中通道 0 和 1 的範例再次落在第一頁,而第二頁的通道 2 到 5 範例則再次落在第一頁。

散佈/收集 DMA 控制器無法正確處理分割音訊畫面的 WavePci 裝置,受限於可以處理的音訊資料格式,雖然軟體因應措施可能有助於減輕某些硬體設計缺陷。 如需詳細資訊,請參閱 WavePci 延遲。