Supportstatus för MT3620

I det här dokumentet beskrivs den aktuella statusen för Azure Sphere-stöd för MediaTek MT3620. Du kan också referera till MT3620 Product Brief, som kan laddas ned på MediaTek MT3620-webbsidan. Dessutom producerar MediaTek användarhandboken för maskinvara för MT3620, som är en detaljerad guide för integrering av MT3620 MCU i din egen maskinvara.

Viktigt

I det här dokumentet innebär inte stöd för närvarande att kundanvändningen av funktionen är begränsad för närvarande, och denna begränsning kommer sannolikt att tas bort i framtiden. Omvänt innebär inte tillgänglig att funktionen inte kan användas av kunder, och denna begränsning kommer sannolikt inte att ändras.

Om du har funktionsförfrågningar eller feedback välkomnar vi dina kommentarer i Azure Sphere-communityforumet.

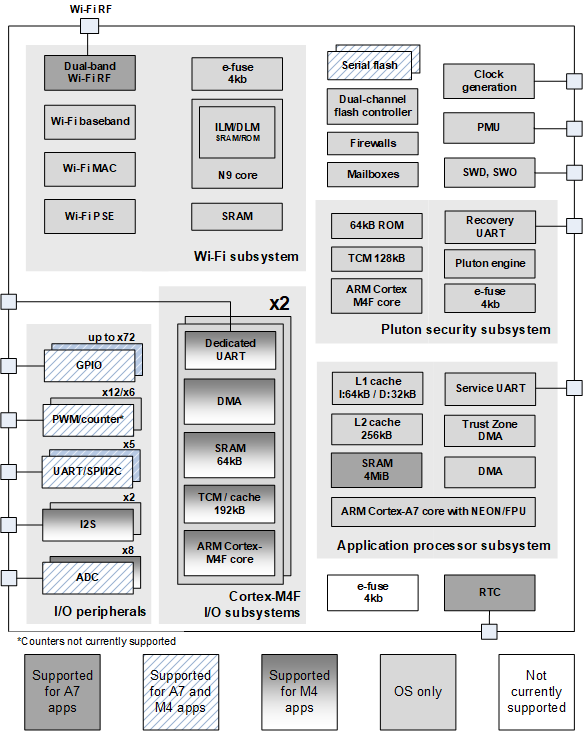

Blockdiagram för MT3620

Blockdiagrammet visar stödet för varje MT3620-komponent. Avsnitten som följer efter diagrammet innehåller ytterligare information om dessa komponenter.

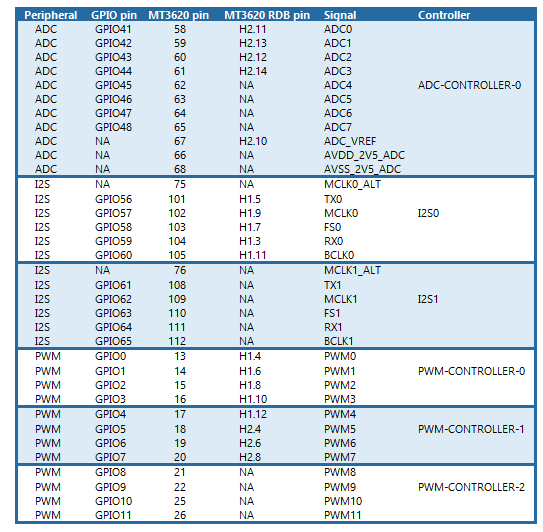

I/O-kringutrustning

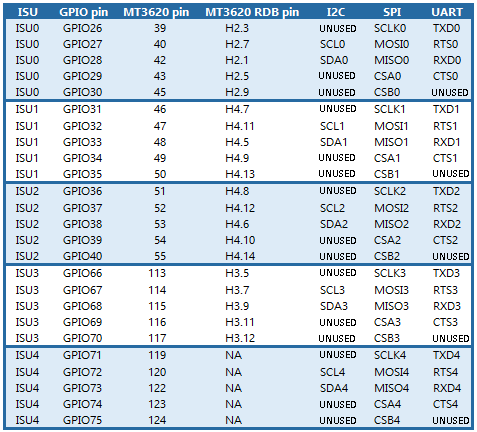

MT3620-designen innehåller totalt 76 programmerbara I/O-stift. Som visas i följande två tabeller är de flesta stiften multiplexerade mellan gpio (general-purpose I/O) och andra funktioner. Utöver GPIO-stiften som anges finns GPIO12-23 på MT3620 stift 27-38 respektive.

Med hänvisning till följande tabell används inte stift som är märkta med "OANVÄND" av den associerade ISU-kringutrustningen och kan konfigureras för användning som GPIO-stift.

Observera

När en ISU-kringutrustning har tilldelats en kärna är alla fem ISU-stift, inklusive oanvända stift, begränsade att användas i den kärnan.

GPIO/PWM/räknare

Vissa stift är multiplexerade mellan GPIO, pulsbreddsmodulering (PWM) och maskinvaruräknare.

GPIO-funktioner som stöds för närvarande är att ange hög/låg utdata och läsinmatning. Öppna avlopp/öppen källkod körlägen och kontroll av enhetens hållfasthet stöds också. Externa avbrott stöds på M4-kärnan men inte på A7-kärnan.

MT3620 har 12 PWM-kanaler, identifierade av PWM0-PWM11. De är ordnade i 3 grupper med 4 kanaler. Varje grupp är associerad med en PWM-styrenhet (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). PWM-kanalerna och GPIO fäster GPIO0 via GPIO11-kartan på samma stift på MT3620. Om programmet använder en PWM-kontroll allokeras alla stift som är kopplade till den kontrollen för användning som PWM-utdata och ingen av dem kan användas för GPIO.

PWM-maskinvaran kan konfigureras för att använda en av tre frekvenser med fast klocka: 32 KHz, 2 MHz (XTAL/13) eller 26 MHz (XTAL). I realtidskärnorna (RT) kan ett realtidsprogram (RTApp) välja vilken klocka som ska användas som bas. På högnivåkärnan (A7) använder Linux-drivrutinen alltid 2 MHz-klockan. Detta resulterar i tjänstcykel- och periodbegränsningar i applikationer på hög nivå, vilket förklaras i Använda PWMs i applikationer på hög nivå.

ISU-block (Serial Interface)

MT3620-designen innehåller fem seriellt gränssnittsblock, som var och en innehåller fem stift. (Dessa block kallas även ISU för "I2C, SPI, UART".) Dessa seriellt gränssnitt block kan multiplex GPIO, universell asynkron mottagare-sändare (UART), interintegrerad krets (I2C) och seriell kringutrustning gränssnitt (SPI).

UART stöds i 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 1152000, 1500000 och 2000000 baud. Det finns en buffert för att ta emot maskinvara med 32 byte. Följande UART-inställningar stöds med 8N1 (8 databitar, 1 stoppbit och ingen paritet) som standardinställning:

- Databit: 5, 6, 7 och 8.

- Stoppbit: 1 och 2.

- Paritet: udda, jämna och inga.

- Flödeskontrollläge: RTS/CTS, XON/XOFF och ingen flödeskontroll.

SPI-transaktioner stöds upp till 40 MHz. Du kan ansluta upp till två underordnade SPI-enheter till varje ISU. När du använder en ISU-port som spi-huvudgränssnitt kan du inte använda samma port som ett I2C- eller UART-gränssnitt. Samtidig dubbelriktad SPI-åtgärder (fullständig dubbelsidig läsning och skrivning) i en enda busstransaktion stöds inte. Följande SPI-inställningar stöds:

- Kommunikationsläge (klockpolaritet, klockfas): SPI-läge 0 (CPOL = 0, CPHA = 0), SPI-läge 1 (CPOL = 0, CPHA = 1), SPI-läge 2 (CPOL = 1, CPHA = 0) och SPI-läge 3 (CPOL = 1, CPHA = 1).

- Bitordning: minst betydande skickas först och mest signifikant skickas först.

- Chip välj polaritet: aktiv-hög, aktiv-låg. Active-low är standardinställningen.

7-bitars underordnade enhetsadresser stöds för I2C. 8-bitars eller 10-bitars I2C underordnade adresser stöds inte. När du använder en ISU-port som I2C-huvudgränssnitt kan du inte använda samma port som ett SPI- eller UART-gränssnitt. I2C-läsningar med 0 byte stöds inte. Följande I2C-inställningar stöds:

- 100 KHz, 400 KHz och 1 MHz busshastigheter.

- Anpassad timeout för åtgärder.

I2S

Två block med fem stift är multiplexerade mellan GPIO och I2S. I2S stöds för närvarande endast för M4-program.

ADC

MT3620 innehåller en 12-bitars ADC med 8 indatakanaler. Ett block med åtta stift är multiplexerat mellan GPIO och ADC. ADC-indatakanalerna och GPIO fäster GPIO41 via GPIO48-kartan på samma stift på MT3260. Men om programmet använder ADC tilldelas alla 8 stift för användning som ADC-indata och ingen av dem kan användas för GPIO.

ARM Barkbark-M4F-undersystem

MT3620 innehåller två delsystem av allmänt syfte ARM Barkbark-M4F, som var och en har ett dedikerat GPIO/UART-block.

MT3620 stöder en standardklockahastighet på 26 MHz. Varje M4-kärna kan dock konfigureras oberoende av varandra för att köras med vilken klockfrekvens som helst mellan 1 MHz och 200 MHz genom att ange dess HCLK_CK_CTRL registrera. Följande kod visar ett sätt att ställa in klockfrekvensen till 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Observera

Mer information om hur du programmerar M4-kärnorna på MT3620 finns i MT3620-dokumentationen som publicerats av MediaTek. Om databladet inte innehåller all information du behöver kan du skicka ett e-postmeddelande till Avnet (Azure.Sphere@avnet.com) för att begära det fullständiga databladet.

ARM-undersystemen Avsteg-M4F kan programmeras för att stödja externa avbrott. Mer information finns i Använda externa avbrott i program som kan användas i realtid .

Programprocessorns undersystem

UNDERsystemet ARM Kernel-A7 kör ett kundprogram tillsammans med Linux-baserade kernel-, -tjänster och -bibliotek från Microsoft.

Tjänsten UART är avsedd för systemfunktioner för A7-undersystemet. Den är inte tillgänglig för användning av kundprogram.

Det engångsprogrammabla e-säkringsblocket, för lagring av enhetsspecifik information, kan inte användas av kundprogram.

Wi-Fi undersystem

Det Wi-Fi delsystemet är för närvarande IEEE 802.11 b/g/n-kompatibelt vid både 2,4 GHz och 5 GHz.

För närvarande har Azure Sphere endast stöd för WPA2, EAP-TLS och öppen autentisering (utan lösenord).

Se RF-testverktyg för information om radiofrekvenstestning och kalibrering.

Energikontroll

MT3620 innehåller power down - och strömprofilfunktioner för att styra energiförbrukningen. Mer information finns i Överväganden om energisparfunktioner och Energiprofil .

Klockor och strömkällor

Huvudkristallen kan för närvarande bara vara 26 MHz. Kristallfrekvenser som inte är 26 MHz stöds för närvarande inte i programvara.

Identifiering av brownout

Brownout-identifiering stöds för närvarande inte.

Timer för maskinvaruvakt

MTK3620 innehåller flera vakthund timers:

- En övervakningstimer dedikerad för användning av Pluton-säkerhetsdomänen. Den här övervakningstimern är inte tillgänglig för användning av program.

- En watchdog timer tillgänglig för programprocessorn. Azure Sphere OS använder den här övervakningstimern för systemtjänster. Den här övervakningstimern är inte tillgänglig för program.

- En övervakningstimer för var och en av realtidskärnana. Dessa övervakningstimers är tillgängliga för realtidsprogram.

Mer information finns i Använda en övervakningstimer i en RTApp .

SWD, SWO

Serial-wire debug (SWD, stift 98-99) stöds endast för M4-program. Serial-wire output (SWO, pin 100) stöds för närvarande inte. Felsökning av ett A7-program stöds av en Gdb-baserad Microsoft-baserad mekanism.

RAM och flash

MT3620 innehåller ungefär 5 MB RAM på die, inklusive 256 KiB i varje I/O-undersystem och 4 MB i A7-programundersystemet.

MT3620 kan beställas med 16 MB SPI-minne.

Mer information om RAM-minne och flash-minne som är tillgängligt för program finns i Minne tillgängligt för program.

Stöd för tillverkningstest

Dokumentation och verktyg som stöder integrering av anpassade tillverkningstestprogram med fabriksprocesser är ännu inte tillgängliga.

Pinut

| Pin# | Fäst namn | Huvudfunktioner | Typ | Beskrivning | Kommentarer |

|---|---|---|---|---|---|

| 1 | GND | P | Marken | ||

| 2 | AVDD_3V3_WF_A_PA | PI | 3,3 V kraftskena för 5 GHz Wi-Fi förstärkare | ||

| 3 | AVDD_3V3_WF_A_PA | PI | 3,3 V kraftskena för 5 GHz Wi-Fi förstärkare | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | 1,6 V kraftskena för Wi-Fi överföring/mottagning | ||

| 7 | AVDD_1V6_WF_AFE | PI | 1,6 V power rail för Wi-Fi analog frontände | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | 1.6V power rail för huvudkristall oscillator | ||

| 10 | MAIN_XIN | AI | Oscillatoringång för huvudkristall | ||

| 11 | WF_ANTSEL0 | GÖRA | Wi-Fi antennval för extern DPDT-omkopplare | ||

| 12 | WF_ANTSEL1 | GÖRA | Wi-Fi antennval för extern DPDT-omkopplare | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 23 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 24 | DVDD_3V3 | PI | 3.3V power rail | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | Avbrotts-kompatibel GPIO multiplexed med PWM-utdata | |

| 27 | GPIO12 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 28 | GPIO13 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 29 | GPIO14 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 30 | GPIO15 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 31 | GPIO16 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 32 | GPIO17 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 33 | GPIO18 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 34 | GPIO19 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 35 | GPIO20 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 36 | GPIO21 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 37 | GPIO22 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 38 | GPIO23 | DIO | Avbrotts-kapabla GPIO | Avbrott stöds för närvarande inte | |

| 39 | GPIO26 | GPIO26/ SCLK0/TXD0 | DIO | GPIO multiplexed med ISU 0-funktioner | |

| 40 | GPIO27 | GPIO27/ MOSI0/RTS0/SCL0 | DIO | GPIO multiplexed med ISU 0-funktioner | |

| 41 | GND | P | Marken | ||

| 42 | GPIO28 | GPIO28/ MISO0/RXD0/SDA0 | DIO | GPIO multiplexed med ISU 0-funktioner | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO multiplexed med ISU 0-funktioner | |

| 44 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO multiplexed med ISU 0-funktioner | |

| 46 | GPIO31 | GPIO31/ SCLK1/TXD1 | DIO | GPIO multiplexed med ÄRU 1-funktioner | |

| 47 | GPIO32 | GPIO32/ MOSI1/RTS1/SCL1 | DIO | GPIO multiplexed med ÄRU 1-funktioner | |

| 48 | GPIO33 | GPIO33/ MISO1/RXD1/SDA1 | DIO | GPIO multiplexed med ÄRU 1-funktioner | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO multiplexed med ÄRU 1-funktioner | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO multiplexed med ÄRU 1-funktioner | |

| 51 | GPIO36 | GPIO36/ SCLK2/TXD2 | DIO | GPIO multiplexed med ISU 2-funktioner | |

| 52 | GPIO37 | GPIO37/ MOSI2/RTS2/SCL2 | DIO | GPIO multiplexed med ISU 2-funktioner | |

| 53 | GPIO38 | GPIO38/ MISO2/RXD2/SDA2 | DIO | GPIO multiplexed med ISU 2-funktioner | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO multiplexed med ISU 2-funktioner | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO multiplexed med ISU 2-funktioner | |

| 56 | DVDD_3V3 | PI | 3.3V power rail | ||

| 57 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO multiplexed med ADC-inmatning | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO multiplexed med ADC-inmatning | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO multiplexed med ADC-inmatning | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO multiplexed med ADC-inmatning | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO multiplexed med ADC-inmatning | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO multiplexed med ADC-inmatning | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO multiplexed med ADC-inmatning | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO multiplexed med ADC-inmatning | |

| 66 | AVDD_2V5_ADC | PI | 2,5 V drivjärn för ADC | ||

| 67 | VREF_ADC | AI | Referensspänning för ADC | ||

| 68 | AVSS_2V5_ADC | P | Mark för ADC | ||

| 69 | EXT_PMU_EN | GÖRA | Extern nätadapter aktiverar utdata | ||

| 70 | WAKEUP | DI | Extern aktivering från djupaste strömsparläge | Stöds inte för närvarande | |

| 71 | AVDD_3V3_RTC | PI | 3.3V power rail för realtidsklocka | ||

| 72 | RTC_XIN | AI | Inmatning av kristalloscillator i realtid | ||

| 73 | RTC_XOUT | AO | Realtime klocka kristall oscillator utgång | ||

| 74 | AVDD_3V3_XPPLL | PI | 3.3V power rail för intern faslåst slinga | ||

| 75 | I2S_MCLK0_ALT | AO | Analogt alternativ till MCLK0 | I2S stöds för närvarande endast för M4-program. | |

| 76 | I2S_MCLK1_ALT | AO | Analogt alternativ till MCLK1 | I2S stöds för närvarande endast för M4-program. | |

| 77 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 78 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 79 | VOUT_2V5 | PO | Utdata från intern 2,5 V LDO | ||

| 80 | AVDD_3V3 | PI | 3.3V power rail | ||

| 81 | PMU_EN | DI | Åsidosättning av intern PMU | ||

| 82 | RESERVERADE | ||||

| 83 | GND | P | Marken | ||

| 84 | SENSE_1V15 | AI | Känna av ingång för att stabilisera 1,15 V-nätadaptern | ||

| 85 | VOUT_1V15 | PO | Utdata från intern 1.15V LDO | ||

| 86 | AVDD_1V6_CLDO | PI | 1,6 V drivjärn för den inre LDO:en med 1,15 V kärnor | ||

| 87 | PMU_CAP | A | Anslut en kondensator mellan stiftet och AVDD_3V3_BUCK för att upprätthålla PMU-stabiliteten | ||

| 88 | AVDD_3V3_BUCK | PI | 3.3V kraftskena för intern 1,6 V buck DC-DC-omvandlare | ||

| 89 | AVDD_3V3_BUCK | PI | 3.3V kraftskena för intern 1,6 V buck DC-DC-omvandlare | ||

| 90 | VOUT_1V6 | PO | Utdata från intern 1,6 V-buck omvandlare | ||

| 91 | VOUT_1V6 | PO | Utdata från intern 1,6 V-buck omvandlare | ||

| 92 | AVSS_3V3_BUCK | P | Jord för intern 1,6 V buck omvandlare | ||

| 93 | AVSS_3V3_BUCK | P | Jord för intern 1,6 V buck omvandlare | ||

| 94 | DEBUG_RXD | DI | Reserverad för Azure Sphere-felsökning | ||

| 95 | DEBUG_TXD | GÖRA | Reserverad för Azure Sphere-felsökning | ||

| 96 | DEBUG_RTS | GÖRA | Reserverad för Azure Sphere-felsökning | ||

| 97 | DEBUG_CTS | DI | Reserverad för Azure Sphere-felsökning | ||

| 98 | SWD_DIO | DIO | ARM SWD för Barken-M4F felsökning | ||

| 99 | SWD_CLK | DI | ARM SWD för Barken-M4F felsökning | ||

| 100 | SWO | GÖRA | ARM SWO för Barken-M4F felsökning | Stöds inte för närvarande | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO multiplexed med I2S 0 | I2S stöds för närvarande endast för M4-program. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO multiplexed med I2S 0 | I2S stöds för närvarande endast för M4-program. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO multiplexed med I2S 0 | I2S stöds för närvarande endast för M4-program. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO multiplexed med I2S 0 | I2S stöds för närvarande endast för M4-program. |

| 105 | GPIO60 | GPIO60/ BCLK0 | DIO | GPIO multiplexed med I2S 0 | I2S stöds för närvarande endast för M4-program. |

| 106 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 107 | DVDD_3V3 | PI | 3.3V power rail | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO multiplexed med I2S 1 | I2S stöds för närvarande endast för M4-program. |

| 109 | GPIO62 | GPIO62/ MCLK1 | DIO | GPIO multiplexed med I2S 1 | I2S stöds för närvarande endast för M4-program. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO multiplexed med I2S 1 | I2S stöds för närvarande endast för M4-program. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO multiplexed med I2S 1 | I2S stöds för närvarande endast för M4-program. |

| 112 | GPIO65 | GPIO65/ BCLK1 | DIO | GPIO multiplexed med I2S 1 | I2S stöds för närvarande endast för M4-program. |

| 113 | GPIO66 | GPIO66/ SCLK3/TXD3 | DIO | GPIO multiplexed med ISU 3-funktioner | |

| 114 | GPIO67 | GPIO67/ MOSI3/RTS3/SCL3 | DIO | GPIO multiplexed med ISU 3-funktioner | |

| 115 | GPIO68 | GPIO68/ MISO3/RXD3/SDA3 | DIO | GPIO multiplexed med ISU 3-funktioner | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO multiplexed med ISU 3-funktioner | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO multiplexed med ISU 3-funktioner | Stöder för närvarande endast GPIO |

| 118 | DVDD_3V3 | PI | 3.3V power rail | ||

| 119 | GPIO71 | GPIO71/ SCLK4/TXD4 | DIO | GPIO multiplexed med ISU 4-funktioner | |

| 120 | GPIO72 | GPIO72/ MOSI4/RTS4/SCL4 | DIO | GPIO multiplexed med ISU 4-funktioner | |

| 121 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 122 | GPIO73 | GPIO73/ MISO4/RXD4/SDA4 | DIO | GPIO multiplexed med ISU 4-funktioner | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO multiplexed med ISU 4-funktioner | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO multiplexed med ISU 4-funktioner | |

| 125 | SYSRST_N | DI | Systemåterställning, låg aktiv | ||

| 126 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 127 | SERVICE_TXD | GÖRA | Azure Sphere-tjänstport | Inte tillgängligt för användning av kundprogram | |

| 128 | SERVICE_RTS | GÖRA | Azure Sphere-tjänstport | Inte tillgängligt för användning av kundprogram | |

| 129 | SERVICE_RXD | DI | Azure Sphere-tjänstport | Inte tillgängligt för användning av kundprogram | |

| 130 | SERVICE_CTS | DI | Azure Sphere-tjänstport | Inte tillgängligt för användning av kundprogram | |

| 131 | RESERVERADE | ||||

| 132 | DVDD_1V15 | PI | 1,15 V kraftstång | ||

| 133 | DVDD_3V3 | PI | 3.3V power rail | ||

| 134 | RECOVERY_RXD | DI | Återställningsport för Azure Sphere | Inte tillgängligt för användning av kundprogram | |

| 135 | RECOVERY_TXD | GÖRA | Återställningsport för Azure Sphere | Inte tillgängligt för användning av kundprogram | |

| 136 | RECOVERY_RTS | GÖRA | Återställningsport för Azure Sphere | Inte tillgängligt för användning av kundprogram | |

| 137 | RECOVERY_CTS | DI | Återställningsport för Azure Sphere | Inte tillgängligt för användning av kundprogram | |

| 138 | IO0_GPIO85 | IO0_GPIO85/ IO0_RXD | DI | Dedikerad GPIO multiplexed med UART för I/O M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/ IO0_TXD | GÖRA | Dedikerad GPIO multiplexed med UART för I/O M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/ IO0_RTS | GÖRA | Dedikerad GPIO multiplexed med UART för I/O M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/ IO0_CTS | DI | Dedikerad GPIO multiplexed med UART för I/O M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/ IO1_RXD | DI | Dedikerad GPIO multiplexed med UART för I/O M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/ IO1_TXD | GÖRA | Dedikerad GPIO multiplexed med UART för I/O M4 1 | |

| 144 | DVDD_3V3 | PI | 3.3V power rail | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/ IO1_RTS | GÖRA | Dedikerad GPIO multiplexed med UART för I/O M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/ IO1_CTS | DI | Dedikerad GPIO multiplexed med UART för I/O M4 1 | |

| 147 | RESERVERADE | ||||

| 148 | TEST | DI | Måste dras lågt för normal drift | ||

| 149 | WF_G_RF_AUXIN | RF | 2,4 GHz-Wi-Fi får mångfaldsport | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | 3,3 V kraftskena för 2,4 GHz Wi-Fi effektförstärkare | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | 2,4 GHz Wi-Fi antennport (differential) | ||

| 154 | WF_G_RF_ION | RF | 2,4 GHz Wi-Fi antennport (differential) | ||

| 155 | WF_G_RF_IOP | RF | 2,4 GHz Wi-Fi antennport (differential) | ||

| 156 | WF_G_RF_IOP | RF | 2,4 GHz Wi-Fi antennport (differential) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | 3,3 V kraftskena för 2,4 GHz Wi-Fi strömöverföring | ||

| 159 | WF_A_RF_AUXIN | RF | 5 GHz-Wi-Fi får mångfaldsport | ||

| 160 | AVDD_3V3_WF_A_TX | PI | 3,3 V kraftskena för 5 GHz Wi-Fi kraftöverföring | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | 5 GHz Wi-Fi antennport (obalanserad) | ||

| 163 | WF_A_RFIO | RF | 5 GHz Wi-Fi antennport (obalanserad) | ||

| 164 | GND | P | Marken | ||

| 165 | EPAD | P | Marken |