Preparar o hardware para o sistema de espera moderno

Ao entrar no sistema de espera moderno, os componentes de hardware devem estar preparados para fazer a transição para a operação de baixa potência. Depois que os componentes de software e os aplicativos tiverem sido preparados para a operação de baixa potência, os componentes de hardware, incluindo seus drivers de dispositivo de software, deverão ser preparados da mesma forma para a operação de baixa potência.

O restante deste artigo explica como preparar os dispositivos fora e dentro do SoC (Sistema em um Chip) para operar em um modo de baixa potência depois que a plataforma de hardware entrar em espera.

Transição de hardware para o modo de baixa potência

Todos os dispositivos dentro e fora do SoC devem entrar em um modo de baixa energia para atingir uma duração longa da bateria enquanto dormem. Depois que uma plataforma de hardware entra em suspensão, os dispositivos na plataforma mudam para modos de baixa potência em um processo ordenado que começa com os dispositivos fora do SoC.

Primeiro, todos os dispositivos fora do SoC ou do silício principal devem entrar em um modo de baixa potência. O modo de energia pode ser um estado ocioso fechado pelo relógio, por exemplo, colocando um controlador de toque anexado a I²C em um modo de suspensão. Ou o modo de energia pode ser um estado de 0 watt de energia chamado D3cold. Uma câmera da Web conectada a USB geralmente fará a transição para D3cold durante o sistema de espera moderno. Para obter mais informações, consulte Suporte a D3cold para dispositivos USB.

Cada classe de dispositivo e barramento de conexão tem sua própria terminologia e requisitos para fazer a transição de um dispositivo para o modo de energia mais baixo. No entanto, é fundamental que um designer de sistema planeje um modo de operação de baixa potência para cada dispositivo na plataforma durante o sistema de espera moderno. A duração da bateria do sistema e a capacidade de colocar o próprio SoC em um modo de baixa energia dependem do gerenciamento correto de energia de cada dispositivo fora do próprio SoC.

Em seguida, os dispositivos de rede e rádio são colocados em um modo de baixa potência para suspensão. Durante a suspensão, esses dispositivos geralmente ainda têm energia aplicada para manter a conectividade e são necessários para ativar o SoC, se necessário. As comunicações e os dispositivos de rádio normalmente entram no estado de baixa potência D2/D3, embora a entrada em cada estado seja específica da classe de dispositivo e específica do barramento.

Depois que todos os dispositivos fora do SoC, incluindo dispositivos de comunicação, tiverem sido desativados, os controladores de host no SoC serão desativados. Quase todos os SoC têm controladores de host USB, I²C, GPIO, SDIO e UART. Cada um desses componentes no SoC deve ser desativado para que o SoC entre em um modo de baixa potência.

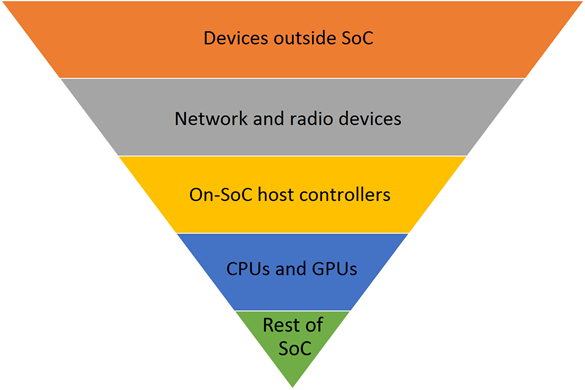

O processo de preparação do hardware para baixa potência durante a suspensão pode ser visualizado como uma pirâmide de cabeça para baixo, conforme mostrado no diagrama a seguir. A menor potência é obtida quando todo o chip do SoC é desativado, mas isso só pode ocorrer depois que cada conjunto de dispositivos acima dele na pirâmide tiver sido desativado.

Desativar os dispositivos fora do SoC

Cada dispositivo fora do chip do SoC deve entrar em um modo de baixa potência para duas finalidades principais:

- Reduzir o consumo de energia do dispositivo.

- Permitir que o próprio SoC seja desativado permitindo que o controlador de host no SoC, ao qual o dispositivo está conectado, seja desativado.

O método para desativar cada dispositivo fora do SoC varia de acordo com a classe de dispositivo e o barramento anexado.

Alguns dispositivos fora do SoC são colocados em um estado de 0 watt, sem consumo de energia, chamado D3cold. Dispositivos comuns para D3cold incluem câmeras e sensores. O driver deve salvar o estado de registro do dispositivo e, em seguida, fazer a transição do dispositivo para o estado de energia D3. A energia será removida pelo firmware ACPI alternando uma linha GPIO ou desativando um trilho de alimentação do PMIC (IC de gerenciamento de energia).

Alguns dispositivos fora do SoC são colocados em um modo ocioso de baixa potência no qual o estado de registro é mantido ou o dispositivo pode simplesmente ser fechado pelo relógio. Por exemplo, muitos controladores de toque apresentam um estado fechado pelo relógio que consome menos de 1 miliwatt de energia. As vantagens típicas de usar um estado fechado pelo relógio são o tempo de ativação mais rápido e o menor custo por não ter que conectar o dispositivo a um trilho de alimentação comutável.

Em geral, todos os dispositivos fora do SoC devem ser capazes de entrar em um modo de baixa potência que consome menos de 1 miliwatt de energia. Os dispositivos que não conseguem atingir esse nível de energia com um estado interno fechado pelo relógio devem implementar a alimentação por meio de D3cold.

Dispositivos de rede e rádio são a exceção notável à diretriz de 1 miliwatt. Dispositivos de rede e rádio podem exigir mais energia para manter uma conexão com a rede ou para ouvir dispositivos sem fio. Alguns designers de sistema chamam essas transições de estado de energia de RUNTIME D3 (RTD3).

Gerenciamento de energia direcionado para dispositivos PCIe

Os cartões PCIe fora do SoC devem habilitar um mecanismo de gerenciamento de energia direcionado chamado Device-S4 para garantir que eles possam entrar em um modo de baixa energia. Sem o Device-S4, se um usuário conectar um dispositivo a uma porta raiz PCIe com slots acessíveis pelo usuário em um sistema de espera moderno da área de trabalho e o driver do dispositivo não oferecer suporte ao runtime D3 (RTD3), o dispositivo PCIe poderá impedir que o sistema insira DRIPS. Para evitar esse problema, os OEMs devem optar pelas Portas Raiz do dispositivo PCIe para o Dispositivo S4. Para que o Dispositivo S4 seja acionado para um determinado dispositivo PCIe, os seguintes requisitos devem ser atendidos:

- A porta raiz PCIe pai para o dispositivo deve ser especificada como uma restrição para DRIPS.

- A porta raiz PCIe pai deve aplicar a redefinição de dispositivo fundamental para todos os filhos downstream da porta raiz após a transição D0->D3 da porta raiz e desabilitar a redefinição de dispositivo fundamental para esses filhos após a transição D3->D0. Para obter mais informações sobre redefinições fundamentais da PCIe, consulte a Seção 6.6.1 da Especificação base do PCI Express. A aplicação da redefinição fundamental pode ser fornecida por mecanismos ACPI complementares. Para obter mais informações, consulte este guia sobre Gerenciamento de energia da PCI. Para indicar que a plataforma respeita esse requisito fundamental de redefinição, o firmware deve definir _DSD com suporte para GUID {FDF06FAD-F744-4451-BB64-ECD792215B10}. Sem isso, o DRIPS direcionado não será disparado para dispositivos nessa porta raiz PCIe. Para obter mais informações, consulte os Dados específicos do dispositivo ACPI (_DSD) para portas raiz PCIe.

- Os recursos de energia devem ser exclusivos para uma determinada porta raiz PCIe, ou seja, não devem ser compartilhados com nenhuma outra porta raiz.

Observe que os cartões de PCIe que exigem CSM (módulos de suporte de compatibilidade) não funcionarão em sistemas de espera modernos. O CSM não tem suporte no BIOS em sistemas de espera modernos devido ao requisito de Inicialização Segura UEFI. Para obter mais informações, consulte a Especificação do Programa de Compatibilidade do Windows.

Para obter mais informações sobre o gerenciamento de energia para classes de dispositivo específicas, os designers de sistema são incentivados a examinar o Gerenciamento de energia específico do dispositivo para sistema de espera moderno, bem como a documentação específica do dispositivo no Microsoft Collaborate.

Desativar dispositivos de rede

Desativar a rede e os dispositivos de rádio é outra parte fundamental da preparação do hardware para a operação de baixa energia durante a suspensão. Os dispositivos de rede e de rádio são diferentes de outros dispositivos fora do SoC porque devem permanecer ativos com a energia aplicada para escutar eventos interessantes e ativar o SoC. Por exemplo, o rádio Wi-Fi deve ser capaz de escutar pacotes que correspondam aos padrões WoL e acordar o SoC quando um pacote correspondente for detectado.

O Windows faz a transição de dispositivos de rede para o estado D2/D3 durante a suspensão, caso se espere que eles ativarão o SoC. A pilha de rede do Windows configurará os padrões WoL e os descarregamentos de protocolo antes de colocar o dispositivo no estado D2/D3 de baixa potência. Todos os dispositivos de rede, incluindo Wi-Fi, banda larga móvel (MBB) e Ethernet com fio, devem ser capazes de entrar no estado D2/D3 durante a suspensão. Se um dispositivo de rede não for necessário para ativar o sistema, o Windows fará a transição do dispositivo para o estado D3. O dispositivo de rede poderá ser colocado no estado D3 se o usuário tiver habilitado o modo avião ou desabilitado o dispositivo de rede específico.

Cada dispositivo tem um método físico diferente para ativar o SoC do modo de energia mais baixo. Espera-se que os dispositivos de rede no SDIO ou UART sinalizem uma linha GPIO para ativar o SoC. Espera-se que os dispositivos de rede conectados via USB ou HSIC usem a sinalização de retomada USB em banda para ativar o SoC. Espera-se que os dispositivos de rede em barramentos PCI ou PCIe usem a sinalização PME em banda para ativar o SoC.

Além disso, um dispositivo de rádio, como um dispositivo Bluetooth ou NFC (comunicações de campo próximo), deverá fazer a transição para o estado D2 se o usuário tiver ligado o rádio para este dispositivo. No estado D2, um rádio Bluetooth escuta eventos de entrada de mouses e teclados emparelhados. Se um evento de entrada for detectado, o rádio Bluetooth alterna uma linha GPIO conectada ao SoC, o que faz com que o SoC seja ativado do modo de baixa potência.

Cada dispositivo de rede ou de rádio tem sua própria implementação de desligar para sistema de espera moderno. Os designers de sistema são incentivados a ler os documentos específicos da classe do dispositivo no site do Microsoft Collaborate.

Desativar controladores de host no SoC

Depois que todos os dispositivos fora do SoC, incluindo dispositivos de rede e rádio, tiverem sido desativados, os controladores de host aos quais os dispositivos estão anexados deverão ser desativados. Os controladores de host comuns incluem USB, PCI, SDIO, GPIO e I²C.

O driver para cada controlador de host pode desligar o hardware somente depois que cada dispositivo conectado ao controlador de host tiver sido desativado. Um exemplo comum é o controlador de host USB. O controlador de host USB só pode ser desativado depois que todos os dispositivos USB conectados a ele tiverem entrado em um estado de suspensão seletiva. Se um controlador de host USB tiver um mouse e um teclado USB conectados, o controlador de host só poderá ser desativado depois que o mouse e o teclado tiverem sido desativados. Se o mouse ou o teclado permanecer ativo, o controlador de host USB também permanecerá ativo.

Todos os controladores de host no SoC devem ser desativados para suspensão para que o próprio SoC seja desativado. Por isso, é fundamental que todos os dispositivos executem o gerenciamento de energia do dispositivo. O próprio SoC só pode ser desativado quando cada controlador de host tiver sido desativado. Os controladores de host só podem ser desativados depois que todos os dispositivos conectados a eles tiverem sido desativados.

Desativar CPUs e GPUs

Em termos de gerenciamento de energia, as CPUs e GPUs no chip do SoC são diferentes de outros dispositivos. As CPUs e GPUs são desativadas como parte da alimentação do próprio SoC, sendo capazes de ser desativadas sempre que não houver nenhuma atividade de software direcionada a elas.

A maior parte da atividade de software no sistema será interrompida por meio dos estágios de preparação detalhados no software Prepare para sistema de espera moderno. Os aplicativos da Microsoft Store serão pausados como parte da fase de PLM. Os aplicativos da área de trabalho serão pausados como parte da conclusão da fase de DAM. As únicas atividades de CPU que permanecem após a plataforma entrar na fase de resiliência são operações ociosas do próprio Windows. Da mesma forma, há pouca atividade de GPU porque todos os aplicativos foram pausados e a tela está desativada.

O Windows gerencia continuamente o estado de energia das CPUs no sistema, mesmo quando a tela está ativada e o usuário está trabalhando com o computador. O mesmo gerenciamento de estado de energia da CPU coloca as CPUs em um modo de baixa potência durante a suspensão. Quando todas as CPUs estão em um modo de baixa potência e todos os controladores de host no SoC são desativados, o próprio SoC pode ser desativado.

Desativar o SoC

Quando todos os controladores de host individuais, CPUs e GPUs no SoC tiverem sido desativados, o Windows determinará se é seguro desativar todo o SoC propriamente dito. O fornecedor do SoC fornece um PEP (plug-in do mecanismo de energia) para informar ao Windows quando todo o estado no SoC tiver sido salvo para que o SoC esteja pronto para entrar em um modo de baixa energia. Para SoCs baseados em Intel, o PEP é fornecido na caixa de entrada.

Cada fornecedor de SoC tem uma implementação diferente de um estado de baixa potência em todo o SoC. Normalmente, esses estados são estados fechados pelo relógio ou por energia, nos quais o conteúdo da memória é preservado na auto-atualização e o sistema pode ser despertado por um temporizador programável e um pequeno número de pinos GPIO que consomem muito pouca energia. O Windows se refere ao estado de energia SoC mais baixo como estado mais profundo da plataforma ociosa de runtime (DRIPS).

O estado DRIPS sempre tem as seguintes características:

- DRIPS é o estado de consumo de energia mais baixo para o SoC, no qual a memória é preservada em um modo de auto-atualização.

- O DRIPS permite que o SoC ative eventos de dispositivos de rede, rádio e entrada.

- Nenhum código de CPU tem permissão para ser executado durante o estado DRIPS.

- Quando o SoC está no estado DRIPS, a plataforma está consumindo a menor quantidade de energia possível durante a suspensão (com exceção das variações no consumo de energia causadas por dispositivos de rede e de rádio).