Status de suporte do MT3620

Importante

Esta é a documentação do Azure Sphere (Legado). O Azure Sphere (Legado) será desativado em 27 de setembro de 2027 e os usuários devem migrar para o Azure Sphere (Integrado) até esse momento. Use o seletor de versão localizado acima do sumário para exibir a documentação do Azure Sphere (Integrado).

Este documento descreve o status atual do suporte do Azure Sphere para o MediaTek MT3620. Você também pode consultar o Resumo do Produto MT3620, que está disponível para download na página da Web da MediaTek MT3620. Além disso, a MediaTek produz o MT3620 Hardware User Guide, que é um guia detalhado para integrar o MT3620 MCU em seu próprio hardware.

Importante

No contexto deste documento, não suportado atualmente significa que o uso do recurso pelo cliente é restrito no momento atual, e essa restrição provavelmente será removida no futuro. Por outro lado, não acessível significa que o recurso não pode ser usado pelos clientes, e é improvável que essa restrição mude.

Se você tiver solicitações de recursos ou comentários, agradecemos seus comentários no fórum da comunidade do Azure Sphere.

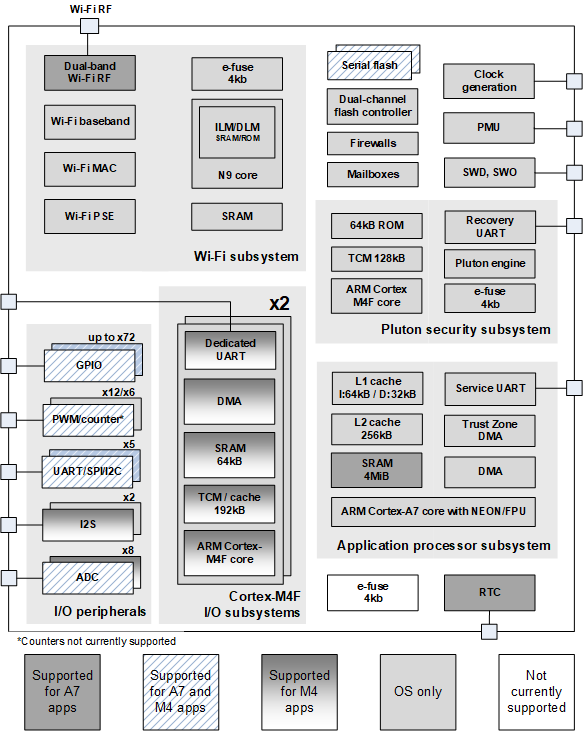

Diagrama de blocos MT3620

O diagrama de blocos mostra o suporte fornecido para cada componente MT3620. As seções que seguem o diagrama fornecem detalhes adicionais sobre esses componentes.

Periféricos de E/S

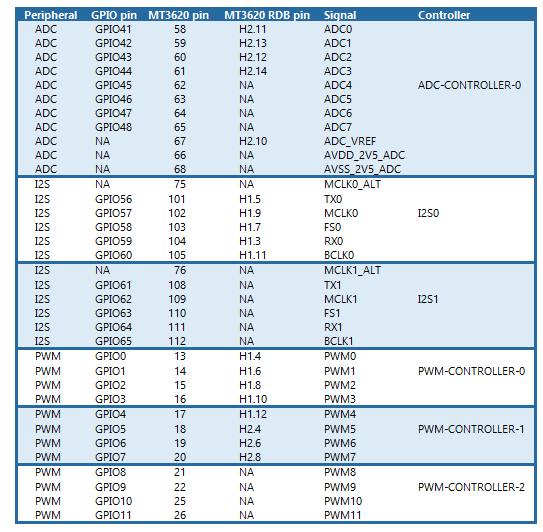

O design MT3620 inclui um total de 76 pinos de E/S programáveis. Como mostrado nas duas tabelas a seguir, a maioria dos pinos são multiplexados entre E/S de uso geral (GPIO) e outras funções. Além dos pinos GPIO listados, GPIO12-23 estão disponíveis em MT3620 pinos 27-38, respectivamente.

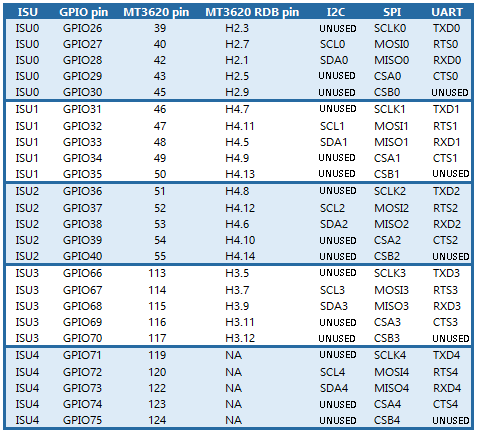

Referindo-se à tabela a seguir, os pinos marcados como "UNUSED" não são usados pelo periférico ISU associado e podem ser configurados para uso como pinos GPIO.

Nota

Uma vez que um periférico ISU tenha sido alocado a um núcleo, todos os 5 pinos ISU, incluindo pinos não utilizados, são restritos ao uso nesse núcleo.

GPIO/PWM/contadores

Alguns pinos são multiplexados entre GPIO, modulação de largura de pulso (PWM) e contadores de hardware.

As funções GPIO atualmente suportadas estão definindo a saída alta/baixa e a entrada de leitura. Os modos de condução de drenagem aberta/código aberto e o controlo da força de acionamento também são suportados. As interrupções externas são suportadas no núcleo M4, mas não no núcleo A7.

A MT3620 tem 12 canais PWM, identificados por PWM0-PWM11. Eles estão organizados em 3 grupos de 4 canais. Cada grupo está associado a um controlador PWM (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). Os canais PWM e GPIO pinos GPIO0 através GPIO11 mapa para os mesmos pinos no MT3620. Se seu aplicativo usa um controlador PWM, todos os pinos associados a esse controlador são alocados para uso como saídas PWM e nenhum deles pode ser usado para GPIO.

O hardware PWM pode ser configurado para usar uma das três frequências de relógio fixo: 32 KHz, 2 MHz (XTAL/13) ou 26 MHz (XTAL). Nos núcleos de tempo real (RT), um aplicativo em tempo real (RTApp) pode selecionar qual relógio usar como base. No núcleo de alto nível (A7), o driver Linux sempre usará o clock de 2 MHz. Isso resulta em limitações de ciclo e período de trabalho em aplicativos de alto nível, conforme explicado em Usar PWMs em aplicativos de alto nível.

Blocos de interface serial (ISU)

O design MT3620 inclui cinco blocos de interface serial, cada um dos quais contém cinco pinos. (Estes blocos também são chamados ISU, para "I2C, SPI, UART.") Estes blocos de interface serial podem multiplex GPIO, universal assíncrono receptor-transmissor (UART), circuito inter-integrado (I2C) e interface periférica serial (SPI).

UART é suportado em 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 1152000, 1500000 e 2000000 baud. Há um buffer de recebimento de hardware de 32 bytes. As seguintes configurações UART são suportadas, com 8N1 (8 bits de dados, 1 bit de parada e sem paridade) como a configuração padrão:

- Bit de dados: 5, 6, 7 e 8.

- Stop bit: 1 e 2.

- Paridade: ímpar, par e nenhum.

- Modo de controle de fluxo: RTS / CTS, XON / XOFF, e sem controle de fluxo.

As transações SPI são suportadas até 40 MHz. Você pode conectar até dois dispositivos SPI subordinados a cada ISU. Quando você usa uma porta ISU como uma interface mestre SPI, você não pode usar a mesma porta que uma interface I2C ou UART. Não há suporte para operações SPI bidirecionais simultâneas de leitura e gravação (full-duplex) em uma única transação de barramento. As seguintes configurações SPI são suportadas:

- Modo de comunicação (polaridade do relógio, fase do relógio): modo SPI 0 (CPOL = 0, CPHA = 0), modo SPI 1 (CPOL = 0, CPHA = 1), modo SPI 2 (CPOL = 1, CPHA = 0) e modo SPI 3 (CPOL = 1, CPHA = 1).

- Ordem de bits: o menos significativo é enviado primeiro, e o mais significativo é enviado primeiro.

- Polaridade de seleção de chip: ativo-alto, ativo-baixo. Ativo-baixo é a configuração padrão.

Os endereços de dispositivos subordinados de 7 bits são suportados para I2C. Não há suporte para endereços subordinados I2C de 8 bits ou 10 bits. Quando você usa uma porta ISU como uma interface mestre I2C, você não pode usar a mesma porta que uma interface SPI ou UART. Não há suporte para leituras I2C de 0 bytes. As seguintes configurações I2C são suportadas:

- Velocidades de barramento de 100 KHz, 400 KHz e 1 MHz.

- Tempo limite personalizado para operações.

I2S

Dois blocos de cinco pinos são multiplexados entre GPIO e I2S. Atualmente, o I2S é suportado apenas para aplicações M4.

ADC

O MT3620 contém um ADC de 12 bits com 8 canais de entrada. Um bloco de oito pinos é multiplexado entre o GPIO e o ADC. Os canais de entrada ADC e os pinos GPIO GPIO41 através GPIO48 mapeiam para os mesmos pinos no MT3260. No entanto, se seu aplicativo usa o ADC, todos os 8 pinos são alocados para uso como entradas ADC e nenhum deles pode ser usado para GPIO.

Subsistemas ARM Cortex-M4F

O MT3620 inclui dois subsistemas ARM Cortex-M4F de uso geral, cada um dos quais tem um bloco GPIO/UART dedicado.

O MT3620 suporta uma taxa de clock padrão de 26 MHz. No entanto, cada núcleo M4 pode ser configurado de forma independente para funcionar em qualquer taxa de clock entre 1 MHz e 200 MHz, definindo seu registro HCLK_CK_CTRL. O código a seguir demonstra uma maneira de definir a taxa de clock para 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Nota

Para obter detalhes sobre a programação dos núcleos M4 no MT3620, consulte a documentação do MT3620 publicada pela MediaTek. Se a folha de dados não contiver todas as informações necessárias, envie um e-mail para Avnet (Azure.Sphere@avnet.com) para solicitar a folha de dados completa.

Os subsistemas ARM Cortex-M4F podem ser programados para suportar interrupções externas. Consulte Usar interrupções externas em aplicativos com capacidade de tempo real para obter detalhes.

Subsistema do processador de aplicativos

O subsistema ARM Cortex-A7 executa um aplicativo do cliente junto com o kernel, serviços e bibliotecas baseados em Linux fornecidos pela Microsoft.

O serviço UART é dedicado à funcionalidade do sistema para o subsistema A7. Ele não está disponível para uso do aplicativo do cliente.

O bloco de fusível eletrônico programável único, para armazenar informações específicas do dispositivo, não pode ser usado por aplicativos do cliente.

Subsistema Wi-Fi

O subsistema Wi-Fi é atualmente compatível com IEEE 802.11 b/g/n em 2,4 GHz e 5 GHz.

Atualmente, o Azure Sphere suporta apenas WPA2, EAP-TLS e autenticação aberta (sem senha).

Consulte Ferramentas de teste de RF para obter informações sobre testes e calibração de radiofrequência.

Controlo de potência

O MT3620 inclui recursos de desligamento e perfil de energia para controlar o consumo de energia. Consulte Considerações sobre desligamento e Considerações sobre perfil de energia para obter detalhes.

Relógios e fontes de alimentação

Atualmente, o cristal principal só pode ser de 26MHz. Frequências de cristal diferentes de 26MHz não são atualmente suportadas no software.

Deteção de brownout

A deteção de brownout não é suportada no momento.

Temporizadores de vigilância de hardware

O MTK3620 inclui vários temporizadores de vigilância:

- Um temporizador de vigilância dedicado para uso pelo domínio de segurança Pluton. Este temporizador de vigilância não está disponível para uso por aplicativos.

- Um temporizador de vigilância disponível para o processador do aplicativo. O SO Azure Sphere utiliza este temporizador de vigilância para serviços do sistema. Este temporizador de vigilância não está disponível para aplicações.

- Um temporizador de vigilância para cada um dos núcleos em tempo real. Estes temporizadores de vigilância estão disponíveis para aplicações em tempo real.

Consulte Usar um temporizador de vigilância em um RTApp para obter mais informações.

SWD, SWO

A depuração de fio serial (SWD, pinos 98-99) é suportada apenas para aplicativos M4. A saída de fio serial (SWO, pino 100) não é suportada no momento. A depuração de um aplicativo A7 é suportada por um mecanismo baseado em gdb fornecido pela Microsoft.

RAM e flash

O MT3620 inclui aproximadamente 5 MB de RAM no die, incluindo 256 KiB em cada subsistema de E/S e 4 MB no subsistema de aplicação A7.

O MT3620 pode ser encomendado com 16 MB de memória flash SPI.

Para obter informações sobre RAM e flash disponíveis para aplicativos, consulte Memória disponível para aplicativos.

Suporte a testes de fabricação

A documentação e os utilitários para dar suporte à integração de aplicativos de teste de fabricação personalizados com os processos de fábrica ainda não estão disponíveis.

Pinagem

| Pino# | Nome do pino | Principais Funções | Tipo | Descrição | Comentários |

|---|---|---|---|---|---|

| 1 | GND | P | Terreno | ||

| 2 | AVDD_3V3_WF_A_PA | PI | Trilho de alimentação de 3,3 V para amplificador de potência Wi-Fi de 5 GHz | ||

| 3 | AVDD_3V3_WF_A_PA | PI | Trilho de alimentação de 3,3 V para amplificador de potência Wi-Fi de 5 GHz | ||

| 4 | N.º | ||||

| 5 | N.º | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Trilho de alimentação de 1,6 V para transmissão/receção Wi-Fi | ||

| 7 | AVDD_1V6_WF_AFE | PI | Trilho de alimentação de 1,6 V para front-end analógico Wi-Fi | ||

| 8 | N.º | ||||

| 9 | AVDD_1V6_XO | PI | Trilho de alimentação de 1.6V para oscilador de cristal principal | ||

| 10 | MAIN_XIN | IA | Entrada do oscilador de cristal principal | ||

| 11 | WF_ANTSEL0 | DO | Seleção de antena Wi-Fi para interruptor DPDT externo | ||

| 12 | WF_ANTSEL1 | DO | Seleção de antena Wi-Fi para interruptor DPDT externo | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 23 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 24 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | GPIO compatível com interrupção multiplexado com saída PWM | |

| 27 | GPIO12 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 28 | GPIO13 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 29 | GPIO14 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 30 | GPIO15 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 31 | GPIO16 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 32 | GPIO17 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 33 | GPIO18 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 34 | GPIO19 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 35 | GPIO20 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 36 | GPIO21 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 37 | GPIO22 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 38 | GPIO23 | DIO | GPIO com capacidade de interrupção | Interrupções não são suportadas atualmente | |

| 39 | GPIO26 | GPIO26/ SCLK0/TXD0 | DIO | GPIO multiplexado com funções ISU 0 | |

| 40 | GPIO27 | GPIO27/ MOSI0/RTS0/SCL0 | DIO | GPIO multiplexado com funções ISU 0 | |

| 41 | GND | P | Terreno | ||

| 42 | GPIO28 | GPIO28/ MISO0/RXD0/SDA0 | DIO | GPIO multiplexado com funções ISU 0 | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO multiplexado com funções ISU 0 | |

| 44 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO multiplexado com funções ISU 0 | |

| 46 | GPIO31 | GPIO31/ SCLK1/TXD1 | DIO | GPIO multiplexado com funções ISU 1 | |

| 47 | GPIO32 | GPIO32/ MOSI1/RTS1/SCL1 | DIO | GPIO multiplexado com funções ISU 1 | |

| 48 | GPIO33 | GPIO33/ MISO1/RXD1/SDA1 | DIO | GPIO multiplexado com funções ISU 1 | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO multiplexado com funções ISU 1 | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO multiplexado com funções ISU 1 | |

| 51 | GPIO36 | GPIO36/ SCLK2/TXD2 | DIO | GPIO multiplexado com funções ISU 2 | |

| 52 | GPIO37 | GPIO37/ MOSI2/RTS2/SCL2 | DIO | GPIO multiplexado com funções ISU 2 | |

| 53 | GPIO38 | GPIO38/ MISO2/RXD2/SDA2 | DIO | GPIO multiplexado com funções ISU 2 | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO multiplexado com funções ISU 2 | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO multiplexado com funções ISU 2 | |

| 56 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 57 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO multiplexado com entrada ADC | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO multiplexado com entrada ADC | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO multiplexado com entrada ADC | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO multiplexado com entrada ADC | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO multiplexado com entrada ADC | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO multiplexado com entrada ADC | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO multiplexado com entrada ADC | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO multiplexado com entrada ADC | |

| 66 | AVDD_2V5_ADC | PI | Trilho de alimentação de 2,5 V para ADC | ||

| 67 | VREF_ADC | IA | Tensão de referência para ADC | ||

| 68 | AVSS_2V5_ADC | P | Terreno para a ADC | ||

| 69 | EXT_PMU_EN | DO | Fonte de alimentação externa permitir saída | ||

| 70 | ACORDAR | SF | Despertar externo do modo de suspensão mais profundo | Não é suportado atualmente | |

| 71 | AVDD_3V3_RTC | PI | Trilho de alimentação de 3,3 V para relógio em tempo real | ||

| 72 | RTC_XIN | IA | Entrada do oscilador de cristal do relógio em tempo real | ||

| 73 | RTC_XOUT | AO | Saída do oscilador de cristal do relógio em tempo real | ||

| 74 | AVDD_3V3_XPPLL | PI | Trilho de alimentação de 3,3 V para circuito interno com bloqueio de fase | ||

| 75 | I2S_MCLK0_ALT | AO | Alternativa analógica ao MCLK0 | Atualmente, o I2S é suportado apenas para aplicações M4. | |

| 76 | I2S_MCLK1_ALT | AO | Alternativa analógica ao MCLK1 | Atualmente, o I2S é suportado apenas para aplicações M4. | |

| 77 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 78 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 79 | VOUT_2V5 | PO | Saída do LDO interno de 2,5 V | ||

| 80 | AVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 81 | PMU_EN | SF | Substituição interna da PMU | ||

| 82 | RESERVADO | ||||

| 83 | GND | P | Terreno | ||

| 84 | SENSE_1V15 | IA | Entrada sensorial para estabilizar a fonte de alimentação de 1,15 V | ||

| 85 | VOUT_1V15 | PO | Saída da LDO interna de 1,15V | ||

| 86 | AVDD_1V6_CLDO | PI | Trilho de alimentação de 1,6 V para o núcleo interno de 1,15 V LDO | ||

| 87 | PMU_CAP | A | Conecte um capacitor entre este pino e AVDD_3V3_BUCK para manter a estabilidade da PMU | ||

| 88 | AVDD_3V3_BUCK | PI | Trilho de alimentação de 3.3V para conversor interno de 1.6V buck DC-DC | ||

| 89 | AVDD_3V3_BUCK | PI | Trilho de alimentação de 3.3V para conversor interno de 1.6V buck DC-DC | ||

| 90 | VOUT_1V6 | PO | Saída do conversor buck interno de 1,6 V | ||

| 91 | VOUT_1V6 | PO | Saída do conversor buck interno de 1,6 V | ||

| 92 | AVSS_3V3_BUCK | P | Terra para conversor interno de buck de 1.6V | ||

| 93 | AVSS_3V3_BUCK | P | Terra para conversor interno de buck de 1.6V | ||

| 94 | DEBUG_RXD | SF | Reservado para depuração do Azure Sphere | ||

| 95 | DEBUG_TXD | DO | Reservado para depuração do Azure Sphere | ||

| 96 | DEBUG_RTS | DO | Reservado para depuração do Azure Sphere | ||

| 97 | DEBUG_CTS | SF | Reservado para depuração do Azure Sphere | ||

| 98 | SWD_DIO | DIO | SWD ARM para depuração Cortex-M4F | ||

| 99 | SWD_CLK | SF | SWD ARM para depuração Cortex-M4F | ||

| 100 | SWO | DO | SWO ARM para depuração do Cortex-M4F | Não é suportado atualmente | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO multiplexado com I2S 0 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO multiplexado com I2S 0 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO multiplexado com I2S 0 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO multiplexado com I2S 0 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 105 | GPIO60 | GPIO60/ BCLK0 | DIO | GPIO multiplexado com I2S 0 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 106 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 107 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO multiplexado com I2S 1 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 109 | GPIO62 | GPIO62/ MCLK1 | DIO | GPIO multiplexado com I2S 1 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO multiplexado com I2S 1 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO multiplexado com I2S 1 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 112 | GPIO65 | GPIO65/ BCLK1 | DIO | GPIO multiplexado com I2S 1 | Atualmente, o I2S é suportado apenas para aplicações M4. |

| 113 | GPIO66 | GPIO66/ SCLK3/TXD3 | DIO | GPIO multiplexado com funções ISU 3 | |

| 114 | GPIO67 | GPIO67/ MOSI3/RTS3/SCL3 | DIO | GPIO multiplexado com funções ISU 3 | |

| 115 | GPIO68 | GPIO68/ MISO3/RXD3/SDA3 | DIO | GPIO multiplexado com funções ISU 3 | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO multiplexado com funções ISU 3 | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO multiplexado com funções ISU 3 | Atualmente suporta apenas GPIO |

| 118 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 119 | GPIO71 | GPIO71/ SCLK4/TXD4 | DIO | GPIO multiplexado com funções ISU 4 | |

| 120 | GPIO72 | GPIO72/ MOSI4/RTS4/SCL4 | DIO | GPIO multiplexado com funções ISU 4 | |

| 121 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 122 | GPIO73 | GPIO73/ MISO4/RXD4/SDA4 | DIO | GPIO multiplexado com funções ISU 4 | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO multiplexado com funções ISU 4 | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO multiplexado com funções ISU 4 | |

| 125 | SYSRST_N | SF | Reposição do sistema, ativo baixo | ||

| 126 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 127 | SERVICE_TXD | DO | Porta de serviço do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 128 | SERVICE_RTS | DO | Porta de serviço do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 129 | SERVICE_RXD | SF | Porta de serviço do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 130 | SERVICE_CTS | SF | Porta de serviço do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 131 | RESERVADO | ||||

| 132 | DVDD_1V15 | PI | Trilho de alimentação de 1.15V | ||

| 133 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 134 | RECOVERY_RXD | SF | Porta de recuperação do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 135 | RECOVERY_TXD | DO | Porta de recuperação do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 136 | RECOVERY_RTS | DO | Porta de recuperação do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 137 | RECOVERY_CTS | SF | Porta de recuperação do Azure Sphere | Não disponível para uso do aplicativo do cliente | |

| 138 | IO0_GPIO85 | IO0_GPIO85/ IO0_RXD | SF | GPIO dedicado multiplexado com UART para E/S M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/ IO0_TXD | DO | GPIO dedicado multiplexado com UART para E/S M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/ IO0_RTS | DO | GPIO dedicado multiplexado com UART para E/S M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/ IO0_CTS | SF | GPIO dedicado multiplexado com UART para E/S M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/ IO1_RXD | SF | GPIO dedicado multiplexado com UART para E/S M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/ IO1_TXD | DO | GPIO dedicado multiplexado com UART para E/S M4 1 | |

| 144 | DVDD_3V3 | PI | Trilho de alimentação de 3.3V | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/ IO1_RTS | DO | GPIO dedicado multiplexado com UART para E/S M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/ IO1_CTS | SF | GPIO dedicado multiplexado com UART para E/S M4 1 | |

| 147 | RESERVADO | ||||

| 148 | TESTAR | SF | Deve ser puxado para baixo para operação normal | ||

| 149 | WF_G_RF_AUXIN | RF | Wi-Fi de 2,4 GHz recebe porta de diversidade | ||

| 150 | N.º | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | Trilho de alimentação de 3,3 V para amplificador de potência Wi-Fi a 2,4 GHz | ||

| 152 | N.º | ||||

| 153 | WF_G_RF_ION | RF | Porta de antena Wi-Fi de 2,4 GHz (diferencial) | ||

| 154 | WF_G_RF_ION | RF | Porta de antena Wi-Fi de 2,4 GHz (diferencial) | ||

| 155 | WF_G_RF_IOP | RF | Porta de antena Wi-Fi de 2,4 GHz (diferencial) | ||

| 156 | WF_G_RF_IOP | RF | Porta de antena Wi-Fi de 2,4 GHz (diferencial) | ||

| 157 | N.º | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | Trilho de alimentação de 3,3 V para transmissão de energia Wi-Fi de 2,4 GHz | ||

| 159 | WF_A_RF_AUXIN | RF | Wi-Fi de 5GHz recebe porta de diversidade | ||

| 160 | AVDD_3V3_WF_A_TX | PI | Trilho de alimentação de 3,3 V para transmissão de energia Wi-Fi de 5 GHz | ||

| 161 | N.º | ||||

| 162 | WF_A_RFIO | RF | Porta de antena Wi-Fi de 5GHz (desequilibrada) | ||

| 163 | WF_A_RFIO | RF | Porta de antena Wi-Fi de 5GHz (desequilibrada) | ||

| 164 | GND | P | Terreno | ||

| 165 | EPAD | P | Terreno |