RSS com interrupções sinalizadas por mensagem

Os drivers de miniport podem dar suporte a MSIs (interrupções sinalizadas por mensagem) para melhorar o desempenho do RSS. As MSIs permitem que a NIC solicite uma interrupção na CPU que processará os dados recebidos. Para obter mais informações sobre o suporte do NDIS para MSI, consulte NDIS MSI-X.

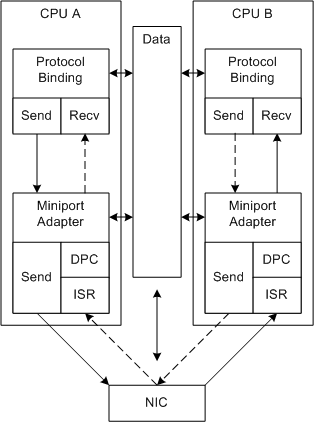

A figura a seguir ilustra o RSS com MSI-X.

Na figura, as setas tracejadas representam o processamento em uma conexão diferente. O RSS com MSI-X permite que a NIC interrompa a CPU correta para uma conexão.

O seguinte processo se repete para cada interrupção:

A NIC:

Usa o DMA para preencher buffers com dados recebidos.

O driver de miniporte alocou os buffers de recebimento na memória compartilhada durante a inicialização.

Calcula um valor de hash.

Enfileira o buffer para uma CPU e fornece as atribuições de fila para o driver de miniporto. Por exemplo, a NIC pode executar um loop das etapas 1 a 3 e DMA uma lista de atribuições de CPU depois que alguns pacotes forem recebidos. O mecanismo específico é deixado para o design nic.

Usando MSI-X, interrompe a CPU associada a uma fila não vazia.

A NIC pode preencher buffers de recebimento adicionais e adicioná-los à fila a qualquer momento, mas não interrompe essa CPU novamente até que o driver de miniporte habilite as interrupções para essa CPU.

O NDIS chama o ISR do driver de miniporto ( MiniportInterrupt) na CPU atual.

O ISR desabilita interrupções na CPU atual e enfileira um DPC na CPU atual.

As interrupções ainda podem ocorrer nas outras CPUs enquanto o DPC está em execução na CPU atual.

O NDIS chama a função MiniportInterruptDPC para cada DPC enfileirado. Cada DPC:

- Os builds recebem descritores para todos os buffers recebidos em sua fila e indica os dados na pilha do driver. Para obter mais informações, consulte Indicando que o RSS recebe dados.

- Habilita interrupções para a CPU atual. Essa interrupção foi concluída e o processo será iniciado novamente. Observe que nenhuma operação atômica é necessária para acompanhar o progresso de outros DPCs.