Stan pomocy technicznej MT3620

Ten dokument zawiera opis bieżącego stanu obsługi usługi Azure Sphere dla programu MediaTek MT3620. Warto również zapoznać się z dokumentacją produktu MT3620, która jest dostępna do pobrania na stronie internetowej MediaTek MT3620. Ponadto mediatek produkuje podręcznik użytkownika sprzętu MT3620, który jest szczegółowym przewodnikiem po integrowaniu MCU MT3620 z własnym sprzętem.

Ważne

W kontekście tego dokumentu obecnie nieobsługiwane oznacza, że korzystanie z tej funkcji przez klientów jest obecnie ograniczone, a to ograniczenie prawdopodobnie zostanie usunięte w przyszłości. Z drugiej strony , niedostępne oznacza, że ta funkcja nie może być używana przez klientów i jest mało prawdopodobne, aby to ograniczenie się zmieniło.

Jeśli masz sugestie dotyczące funkcji lub opinie, z zadowoleniem przyjmujemy Twoje komentarze na forum społeczności azure sphere.

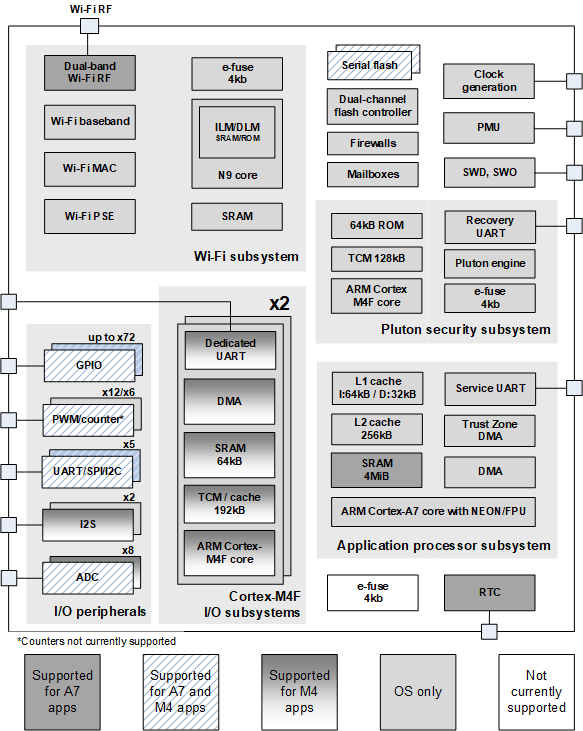

MT3620 block diagram

Diagram blokowy przedstawia obsługę każdego składnika MT3620. Sekcje, które następują po diagramie, zawierają dodatkowe szczegóły dotyczące tych składników.

Urządzenia peryferyjne we/wy

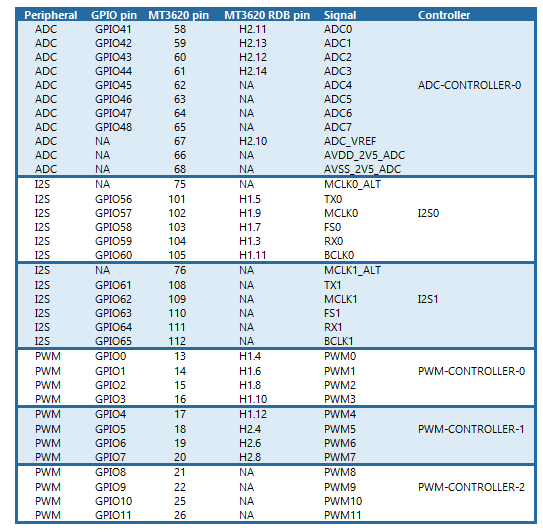

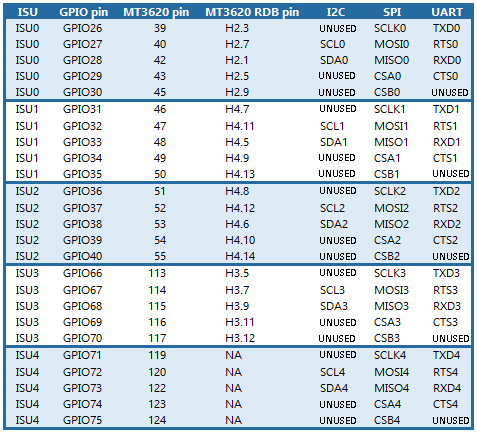

Projekt MT3620 zawiera łącznie 76 programowalnych pinów we/wy. Jak pokazano w dwóch poniższych tabelach, większość pinezki zawiera multipleksowane elementy we/wy ogólnego przeznaczenia (GPIO) i inne funkcje. Oprócz wymienionych pinów GPIO, GPIO12-23 są dostępne odpowiednio na pinach MT3620 27-38.

Odwołując się do poniższej tabeli, pinezki oznaczone jako "UNUSED" nie są używane przez skojarzone urządzenie peryferyjne ISU i można je skonfigurować do używania jako pinezki GPIO.

Uwaga

Po przypisaniu urządzenia peryferyjnego ISU do rdzenia wszystkie 5 pinów ISU, w tym nieużywane styki, jest ograniczonych do używania w tym rdzeniu.

GPIO/PWM/liczniki

Niektóre styki są multipleksowane między gpio, modulacja szerokości impulsów (PWM) i licznikami sprzętowymi.

Obecnie obsługiwane funkcje GPIO ustawiają wartości wyjściowe o wysokiej/niskiej wartości i odczytują dane wejściowe. Otwarte opróżnianie/open source tryby jazdy i kontrola siły dysku są również obsługiwane. Przerwania zewnętrzne są obsługiwane w rdzeniu M4, ale nie w rdzeniu A7.

Mt3620 ma 12 kanałów PWM oznaczonych przez pwm0-PWM11. Są one zorganizowane w 3 grupy po 4 kanały. Każda grupa jest skojarzona z kontrolerem programu PWM (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). Kanały pwm i gpio przypina gpio0 przez GPIO11 map do tych samych pinezki na MT3620. Jeśli aplikacja korzysta z kontrolera programu PWM, wszystkie pinezki skojarzone z tym kontrolerem są przydzielane do użytku jako wyjścia programu PWM i żaden z nich nie może być używany na potrzeby obiektu GPIO.

Sprzęt PWM można skonfigurować do używania jednej z trzech częstotliwości o stałej częstotliwości zegara: 32 KHz, 2 MHz (XTAL/13) lub 26 MHz (XTAL). Na rdzeniach czasu rzeczywistego (RT) aplikacja w czasie rzeczywistym (RTApp) może wybrać zegar, który ma być używany jako podstawa. W przypadku rdzenia wysokiego poziomu (A7) sterownik systemu Linux zawsze będzie używać zegara 2 MHz. Skutkuje to ograniczeniami cyklu cła i okresów w aplikacjach wysokiego poziomu, jak wyjaśniono w temacie Używanie aplikacji PWM w aplikacjach wysokiego poziomu.

Bloki interfejsu szeregowego (ISU)

Projekt MT3620 zawiera pięć szeregowych bloków interfejsu, z których każdy zawiera pięć pinezków. (Te bloki są również nazywane ISU dla "I2C, SPI, UART"). Te szeregowe bloki interfejsu mogą multipleksować GPIO, uniwersalny asynchroniczny nadajnik-odbiornik (UART), układ scalony (I2C) i szeregowy interfejs peryferyjny (SPI).

Funkcja UART jest obsługiwana w systemach 1200, 2400, 4800, 9600, 19200, 38400, 57600, 115200, 230400, 460800, 500000, 576000, 921600, 1000000, 1152000, 1500000 i 2000000. Istnieje 32-bajtowy bufor odbioru sprzętu. Następujące ustawienia grafiki UART są obsługiwane z ustawieniem domyślnym 8N1 (8 bitów danych, 1 bit zatrzymania i bez parzystości):

- Bit danych: 5, 6, 7 i 8.

- Zatrzymaj bit: 1 i 2.

- Parzystość: nieparzysta, parzysta i żadna.

- Tryb sterowania przepływem: RTS/CTS, XON/XOFF i brak sterowania przepływem.

Obsługiwane są transakcje SPI do 40 MHz. Do każdego isu można podłączyć maksymalnie dwa podrzędne urządzenia SPI. Jeśli używasz portu ISU jako interfejsu głównego SPI, nie możesz użyć tego samego portu co interfejs I2C lub UART. Jednoczesne dwukierunkowe operacje odczytu i zapisu (full-duplex) SPI w ramach jednej transakcji magistrali nie są obsługiwane. Obsługiwane są następujące ustawienia SPI:

- Tryb komunikacji (polaryzacja zegara, faza zegara): tryb SPI 0 (CPOL = 0, CPHA = 0), tryb SPI 1 (CPOL = 0, CPHA = 1), tryb SPI 2 (CPOL = 1, CPHA = 0) i tryb SPI 3 (CPOL = 1, CPHA = 1).

- Kolejność bitów: najpierw wysyłana jest najmniejsza istotna wartość, a najpierw wysyłana jest największa wartość.

- Chip wybierz polaryzację: aktywny-wysoki, aktywny-niski. Ustawieniem domyślnym jest wartość Aktywna-niska.

Adresy urządzeń podrzędnych w wersji 7-bitowej są obsługiwane w przypadku I2C. 8-bitowe lub 10-bitowe adresy podrzędne I2C nie są obsługiwane. Jeśli używasz portu ISU jako interfejsu głównego I2C, nie możesz użyć tego samego portu co interfejs SPI lub UART. 0-bajtowe odczyty I2C nie są obsługiwane. Obsługiwane są następujące ustawienia I2C:

- częstotliwości 100 KHz, 400 KHz i 1 MHz.

- Niestandardowy limit czasu dla operacji.

I2S

Dwa bloki z pięcioma pinezkami są multipleksowane między obiektami GPIO i I2S. Obecnie program I2S jest obsługiwany tylko w aplikacjach M4.

ADC

MT3620 zawiera 12-bitową usługę ADC z 8 kanałami wejściowymi. Blok z ośmioma pinezkami jest multipleksowany między obiektem GPIO a usługą ADC. Kanały wejściowe ADC i gpio przypina gpio41 do GPIO48 mapować do tych samych pinezki na MT3260. Jeśli jednak aplikacja korzysta z usługi ADC, wszystkie 8 pinów zostanie przydzielonych do użycia jako dane wejściowe usługi ADC i żaden z nich nie może być używany dla obiektu GPIO.

Podsystemy ARM Cortex-M4F

Mt3620 zawiera dwa podsystemy ARM Cortex-M4F ogólnego przeznaczenia, z których każdy ma dedykowany blok GPIO/UART.

Mt3620 obsługuje domyślną częstotliwość zegara 26 MHz. Każdy rdzeń M4 można jednak skonfigurować tak, aby działał z częstotliwością od 1 MHz do 200 MHz, ustawiając rejestr HCLK_CK_CTRL. Poniższy kod przedstawia jeden ze sposobów ustawienia częstotliwości zegara na 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Uwaga

Aby uzyskać szczegółowe informacje na temat programowania rdzeni M4 na MT3620, zobacz dokumentację MT3620 opublikowaną przez MediaTek. Jeśli arkusz danych nie zawiera wszystkich potrzebnych informacji, wyślij wiadomość e-mail do Avnet (Azure.Sphere@avnet.com), aby zażądać pełnego arkusza danych.

Podsystemy ARM Cortex-M4F można zaprogramować w celu obsługi przerwań zewnętrznych. Aby uzyskać szczegółowe informacje, zobacz Używanie przerwań zewnętrznych w aplikacjach z obsługą czasu rzeczywistego .

Podsystem procesora aplikacji

Podsystem ARM Cortex-A7 obsługuje aplikację klienta wraz z jądrem, usługami i bibliotekami dostarczaną przez firmę Microsoft z systemu Linux.

Usługa UART jest przeznaczona dla funkcji systemowych podsystemu A7. Nie jest ona dostępna do użytku z aplikacjami klientów.

Programowalny blok e-bezpiecznika jednorazowy do przechowywania informacji specyficznych dla urządzenia nie może być używany przez aplikacje klientów.

podsystem Wi-Fi

Podsystem Wi-Fi jest obecnie zgodny ze standardem IEEE 802.11 b/g/n przy częstotliwości 2,4 GHz i 5 GHz.

Obecnie usługa Azure Sphere obsługuje tylko uwierzytelnianie WPA2, EAP-TLS i otwieranie (bez hasła).

Zobacz Narzędzia do testowania fal radiowych, aby uzyskać informacje na temat testowania i kalibracji częstotliwości radiowej.

Kontrolka zasilania

Mt3620 zawiera funkcje power down i profil zasilania do sterowania zużyciem energii. Aby uzyskać szczegółowe informacje, zobacz Zagadnienia dotyczące dodatku Power Down i Zagadnienia dotyczące dodatku Power Profile .

Zegary i źródła zasilania

Główny kryształ może być obecnie tylko 26 MHz. Częstotliwości kryształów inne niż 26 MHz nie są obecnie obsługiwane w oprogramowaniu.

Wykrywanie brownouta

Wykrywanie brownout nie jest obecnie obsługiwane.

Czasomierze strażnika sprzętu

MTK3620 zawiera kilka czasomierzy watchdog:

- Jeden czasomierz watchdog dedykowany do użytku przez domenę bezpieczeństwa Pluton. Ten czasomierz strażnika nie jest dostępny do użycia przez aplikacje.

- Jeden czasomierz watchdog dostępny dla procesora aplikacji. System operacyjny Azure Sphere używa tego czasomierza strażnika do obsługi usług systemowych. Ten czasomierz strażnika nie jest dostępny dla aplikacji.

- Czasomierz strażnika dla każdego rdzenia w czasie rzeczywistym. Te czasomierze watchdog są dostępne dla aplikacji w czasie rzeczywistym.

Aby uzyskać więcej informacji, zobacz Używanie czasomierza strażnika w aplikacji RTApp .

SWD, SWO

Debugowanie szeregowe (SWD, piny 98-99) jest obsługiwane tylko w aplikacjach M4. Wyjście z przewodu szeregowego (SWO, pin 100) nie jest obecnie obsługiwane. Debugowanie aplikacji A7 jest obsługiwane przez dostarczony przez firmę Microsoft mechanizm oparty na gdb.

Pamięć RAM i lampa błyskowa

Mt3620 zawiera około 5 MB pamięci RAM na diecie, w tym 256 KiB w każdym podsystemie we/wy i 4 MB w podsystemie aplikacji A7.

Mt3620 można zamówić z 16 MB pamięci flash SPI.

Aby uzyskać informacje o pamięci RAM i lampie błyskowej dostępnej dla aplikacji, zobacz Pamięć dostępna dla aplikacji.

Pomoc techniczna dotycząca testowania produkcji

Dokumentacja i narzędzia wspomagające integrację niestandardowych aplikacji testowych produkcji z procesami fabrycznymi nie są jeszcze dostępne.

Pinout

| Pin# | Przypnij nazwę | Główne funkcje | Typu | Opis | Komentarze |

|---|---|---|---|---|---|

| 1 | GND | P | Ziemi | ||

| 2 | AVDD_3V3_WF_A_PA | PI | Szyna zasilana 3,3 V dla wzmacniacza zasilania 5 GHz Wi-Fi | ||

| 3 | AVDD_3V3_WF_A_PA | PI | Szyna zasilana 3,3 V dla wzmacniacza zasilania 5 GHz Wi-Fi | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | Szyna zasilana 1,6 V do przesyłania/odbierania Wi-Fi | ||

| 7 | AVDD_1V6_WF_AFE | PI | Szyna zasilana 1,6 V do Wi-Fi analogowego przedniego krańca | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | Szyna zasilana 1,6 V do głównego oscylatora kryształowego | ||

| 10 | MAIN_XIN | AI | Główne dane wejściowe oscylatora kryształowego | ||

| 11 | WF_ANTSEL0 | ZROBIĆ | Wi-Fi antena wybierz zewnętrzny przełącznik DPDT | ||

| 12 | WF_ANTSEL1 | ZROBIĆ | Wi-Fi antena wybierz zewnętrzny przełącznik DPDT | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 23 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 24 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | Wielokropek gpio z obsługą przerwań z wynikami programu PWM | |

| 27 | GPIO12 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 28 | GPIO13 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 29 | GPIO14 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 30 | GPIO15 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 31 | GPIO16 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 32 | GPIO17 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 33 | GPIO18 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 34 | GPIO19 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 35 | GPIO20 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 36 | GPIO21 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 37 | GPIO22 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 38 | GPIO23 | DIO | GpIO z obsługą przerwań | Przerwania nie są obecnie obsługiwane | |

| 39 | GPIO26 | GPIO26/ SCLK0/TXD0 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 0 | |

| 40 | GPIO27 | GPIO27/ MOSI0/RTS0/SCL0 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 0 | |

| 41 | GND | P | Ziemi | ||

| 42 | GPIO28 | GPIO28/ MISO0/RXD0/SDA0 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 0 | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 0 | |

| 44 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 0 | |

| 46 | GPIO31 | GPIO31/ SCLK1/TXD1 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 1 | |

| 47 | GPIO32 | GPIO32/ MOSI1/RTS1/SCL1 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 1 | |

| 48 | GPIO33 | GPIO33/ MISO1/RXD1/SDA1 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 1 | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 1 | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 1 | |

| 51 | GPIO36 | GPIO36/ SCLK2/TXD2 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 2 | |

| 52 | GPIO37 | GPIO37/ MOSI2/RTS2/SCL2 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 2 | |

| 53 | GPIO38 | GPIO38/ MISO2/RXD2/SDA2 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 2 | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 2 | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 2 | |

| 56 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 57 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | Wielokropek GPIO z danymi wejściowymi ADC | |

| 66 | AVDD_2V5_ADC | PI | Szyna zasilana 2,5 V dla ADC | ||

| 67 | VREF_ADC | AI | Napięcie odniesienia dla ADC | ||

| 68 | AVSS_2V5_ADC | P | Podstawa dla usługi ADC | ||

| 69 | EXT_PMU_EN | ZROBIĆ | Zewnętrzny zasilacz umożliwia wyjście | ||

| 70 | WAKEUP | DI | Wznawianie zewnętrzne z najgłębszego trybu uśpienia | Obecnie nieobsługiwane | |

| 71 | AVDD_3V3_RTC | PI | Szyna zasilana 3,3 V do zegara w czasie rzeczywistym | ||

| 72 | RTC_XIN | AI | Dane wejściowe kryształowego oscylatora zegara w czasie rzeczywistym | ||

| 73 | RTC_XOUT | AO | Dane wyjściowe kryształowego oscylatora zegara w czasie rzeczywistym | ||

| 74 | AVDD_3V3_XPPLL | PI | Szyna zasilana 3,3 V do wewnętrznej pętli z blokadą fazową | ||

| 75 | I2S_MCLK0_ALT | AO | Analogowa alternatywa dla MCLK0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. | |

| 76 | I2S_MCLK1_ALT | AO | Analogowa alternatywa dla MCLK1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. | |

| 77 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 78 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 79 | VOUT_2V5 | Zamówienia zakupu | Dane wyjściowe z wewnętrznej 2,5 V LDO | ||

| 80 | AVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 81 | PMU_EN | DI | Wewnętrzne zastępowanie pmu | ||

| 82 | ZASTRZEŻONE | ||||

| 83 | GND | P | Ziemi | ||

| 84 | SENSE_1V15 | AI | Sygnał wejściowy czujnika stabilizujący zasilacz 1,15 V | ||

| 85 | VOUT_1V15 | Zamówienia zakupu | Dane wyjściowe z wewnętrznej aplikacji LDO 1,15 V | ||

| 86 | AVDD_1V6_CLDO | PI | Szyna zasilana 1,6 V do wewnętrznego 1,15 V rdzenia LDO | ||

| 87 | PMU_CAP | A | Podłącz kondensator między tym pinezką a AVDD_3V3_BUCK, aby zachować stabilność pmu | ||

| 88 | AVDD_3V3_BUCK | PI | Szyna zasilana 3,3 V do wewnętrznego konwertera DC-DC 1,6 V | ||

| 89 | AVDD_3V3_BUCK | PI | Szyna zasilana 3,3 V do wewnętrznego konwertera DC-DC 1,6 V | ||

| 90 | VOUT_1V6 | Zamówienia zakupu | Wyjście z wewnętrznego konwertera 1,6 V złotówki | ||

| 91 | VOUT_1V6 | Zamówienia zakupu | Wyjście z wewnętrznego konwertera 1,6 V złotówki | ||

| 92 | AVSS_3V3_BUCK | P | Grunt do wewnętrznego konwertera 1,6 V złotówki | ||

| 93 | AVSS_3V3_BUCK | P | Grunt do wewnętrznego konwertera 1,6 V złotówki | ||

| 94 | DEBUG_RXD | DI | Zarezerwowane dla debugowania usługi Azure Sphere | ||

| 95 | DEBUG_TXD | ZROBIĆ | Zarezerwowane dla debugowania usługi Azure Sphere | ||

| 96 | DEBUG_RTS | ZROBIĆ | Zarezerwowane dla debugowania usługi Azure Sphere | ||

| 97 | DEBUG_CTS | DI | Zarezerwowane dla debugowania usługi Azure Sphere | ||

| 98 | SWD_DIO | DIO | ARM SWD do debugowania Cortex-M4F | ||

| 99 | SWD_CLK | DI | ARM SWD do debugowania Cortex-M4F | ||

| 100 | SWO | ZROBIĆ | ARM SWO dla debugowania Cortex-M4F | Obecnie nieobsługiwane | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | Wielokropek GPIO z systemem I2S 0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | Wielokropek GPIO z systemem I2S 0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | Wielokropek GPIO z systemem I2S 0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | Wielokropek GPIO z systemem I2S 0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 105 | GPIO60 | GPIO60/ BCLK0 | DIO | Wielokropek GPIO z systemem I2S 0 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 106 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 107 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | Wielokropek GPIO z systemem I2S 1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 109 | GPIO62 | GPIO62/ MCLK1 | DIO | Wielokropek GPIO z systemem I2S 1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | Wielokropek GPIO z systemem I2S 1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | Wielokropek GPIO z systemem I2S 1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 112 | GPIO65 | GPIO65/ BCLK1 | DIO | Wielokropek GPIO z systemem I2S 1 | Obecnie program I2S jest obsługiwany tylko w aplikacjach M4. |

| 113 | GPIO66 | GPIO66/ SCLK3/TXD3 | DIO | Wielokropek GPIO z funkcjami ISU 3 | |

| 114 | GPIO67 | GPIO67/ MOSI3/RTS3/SCL3 | DIO | Wielokropek GPIO z funkcjami ISU 3 | |

| 115 | GPIO68 | GPIO68/ MISO3/RXD3/SDA3 | DIO | Wielokropek GPIO z funkcjami ISU 3 | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | Wielokropek GPIO z funkcjami ISU 3 | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | Wielokropek GPIO z funkcjami ISU 3 | Obecnie obsługuje tylko gpio |

| 118 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 119 | GPIO71 | GPIO71/ SCLK4/TXD4 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 4 | |

| 120 | GPIO72 | GPIO72/ MOSI4/RTS4/SCL4 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 4 | |

| 121 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 122 | GPIO73 | GPIO73/ MISO4/RXD4/SDA4 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 4 | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 4 | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | Obiekt GPIO multipleksowany z funkcjami ISU 4 | |

| 125 | SYSRST_N | DI | Resetowanie systemu, aktywne minimum | ||

| 126 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 127 | SERVICE_TXD | ZROBIĆ | Port usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 128 | SERVICE_RTS | ZROBIĆ | Port usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 129 | SERVICE_RXD | DI | Port usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 130 | SERVICE_CTS | DI | Port usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 131 | ZASTRZEŻONE | ||||

| 132 | DVDD_1V15 | PI | Szyna zasilana 1,15 V | ||

| 133 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 134 | RECOVERY_RXD | DI | Port odzyskiwania usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 135 | RECOVERY_TXD | ZROBIĆ | Port odzyskiwania usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 136 | RECOVERY_RTS | ZROBIĆ | Port odzyskiwania usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 137 | RECOVERY_CTS | DI | Port odzyskiwania usługi Azure Sphere | Niedostępne do użytku z aplikacjami klientów | |

| 138 | IO0_GPIO85 | IO0_GPIO85/IO0_RXD | DI | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/IO0_TXD | ZROBIĆ | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/IO0_RTS | ZROBIĆ | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/IO0_CTS | DI | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/IO1_RXD | DI | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/IO1_TXD | ZROBIĆ | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 1 | |

| 144 | DVDD_3V3 | PI | Szyna zasilana 3,3 V | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/IO1_RTS | ZROBIĆ | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/IO1_CTS | DI | Dedykowany obiekt GPIO multiplexed z grafiką UART dla we/wy M4 1 | |

| 147 | ZASTRZEŻONE | ||||

| 148 | TEST | DI | Musi być wyciągnął nisko do normalnego działania | ||

| 149 | WF_G_RF_AUXIN | RF | 2,4 GHz Wi-Fi odbierać port różnorodności | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | Szyna zasilana 3,3 V dla wzmacniacza zasilania 2,4 GHz Wi-Fi | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | Port anteny 2,4 GHz Wi-Fi (różnicowy) | ||

| 154 | WF_G_RF_ION | RF | Port anteny 2,4 GHz Wi-Fi (różnicowy) | ||

| 155 | WF_G_RF_IOP | RF | Port anteny 2,4 GHz Wi-Fi (różnicowy) | ||

| 156 | WF_G_RF_IOP | RF | Port anteny 2,4 GHz Wi-Fi (różnicowy) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | Szyna zasilana 3,3 V do transmisji energii 2,4 GHz Wi-Fi | ||

| 159 | WF_A_RF_AUXIN | RF | 5 GHz Wi-Fi odbierać port różnorodności | ||

| 160 | AVDD_3V3_WF_A_TX | PI | Szyna zasilana 3,3 V do transmisji energii 5 GHz Wi-Fi | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | Port anteny 5 GHz Wi-Fi (niezrównoważony) | ||

| 163 | WF_A_RFIO | RF | Port anteny 5 GHz Wi-Fi (niezrównoważony) | ||

| 164 | GND | P | Ziemi | ||

| 165 | EPAD | P | Ziemi |