RSS met één hardware-ontvangstwachtrij

Miniportstuurprogramma's kunnen RSS voor NIC's ondersteunen die ondersteuning bieden voor RSS-hashberekening en één ontvangendescriptorwachtrij.

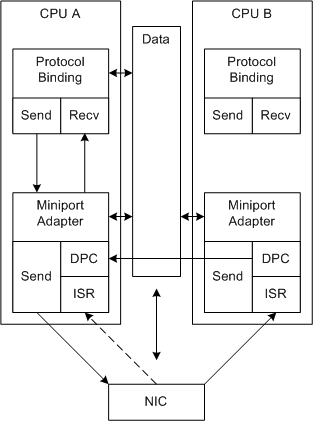

In de volgende afbeelding ziet u RSS-verwerking met één ontvangstdescriptorwachtrij.

In de afbeelding vertegenwoordigen de stippelpijlen een alternatief pad voor de ontvangstverwerking. RSS kan de CPU die de eerste ISR-aanroep ontvangt, niet beheren.

In tegenstelling tot de verwerking van niet-RSS-ontvangst, wordt de ontvangstverwerking op basis van RSS verdeeld over meerdere CPU's. De verwerking voor een bepaalde verbinding kan ook worden gekoppeld aan een bepaalde CPU.

Het volgende proces wordt herhaald voor elke interrupt:

De NIC gebruikt DMA om buffers te vullen met ontvangen gegevens en onderbreekt het systeem.

Tijdens de initialisatie heeft het minipoortstuurprogramma de ontvangstbuffers in het gedeelde geheugen toegewezen.

De NIC kan op elk gewenst moment extra ontvangstbuffers invullen, maar niet opnieuw onderbreken totdat het minipoortstuurprogramma de interrupts inschakelt.

De ontvangen buffers die door het systeem in één interrupt worden verwerkt, kunnen worden gekoppeld aan veel verschillende netwerkverbindingen.

NDIS roept de MiniportInterrupt functie (ISR) van de miniportstuurprogrammadriver aan op een door het systeem bepaalde CPU.

De ISR schakelt de interrupts uit en vraagt NDIS om een uitgestelde procedureaanroep (DPC) in de wachtrij te plaatsen om de ontvangen gegevens te verwerken.

NDIS roept de MiniportInterruptDPC functie (DPC) aan op de huidige CPU. In de DPC:

- Het minipoortstuurprogramma gebruikt de hashwaarden die de NIC heeft berekend voor elke ontvangen buffer en wijs elke ontvangen buffer opnieuw toe aan een ontvangstwachtrij die is gekoppeld aan een CPU.

- De huidige DPC vraagt NDIS om een DPC in de wachtrij te plaatsen voor elk van de andere CPU's die zijn gekoppeld aan een niet-lege ontvangstwachtrij.

- Als de huidige DPC wordt uitgevoerd op een CPU die is gekoppeld aan een niet-lege wachtrij, verwerkt de huidige DPC de bijbehorende ontvangbuffers en stuurt de ontvangen gegevens door in de driver stack.

Voor het toewijzen van wachtrijen en het in wachtrij plaatsen van extra DPC's is extra verwerkingsoverhead vereist. Om betere systeemprestaties te bereiken, moet deze overhead worden verschoven door een beter gebruik van beschikbare CPU's.

De DPC op een bepaalde CPU:

- Verwerkt de ontvangstbuffers die zijn gekoppeld aan de ontvangstwachtrij en geeft de gegevens door in de stuurprogrammastack. Voor meer informatie, zie Indicatie van Rss-ontvangstgegevens.

- Hiermee schakelt u de onderbrekingen in als dit de laatste DPC is om af te ronden. Deze interrupt is voltooid en het proces wordt opnieuw gestart. Het stuurprogramma moet een atomische bewerking gebruiken om de laatste DPC te identificeren die moet worden voltooid. Het stuurprogramma kan bijvoorbeeld de NdisInterlockedDecrement functie gebruiken om een atomische teller te implementeren.