맵 레지스터

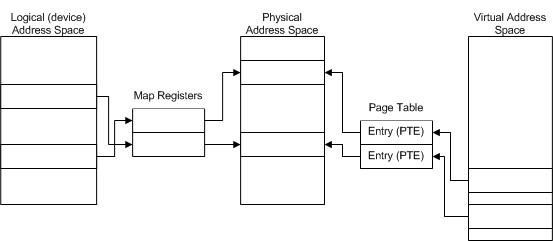

DMA를 수행하는 드라이버는 다음 그림과 같이 세 가지 주소 공간을 사용합니다.

모든 Windows 플랫폼에서 드라이버는 프로세서에서 지원하는 전체 가상 주소 공간에 액세스할 수 있습니다. 32비트 프로세서에서 가상 주소 공간은 4GB를 나타냅니다. CPU는 페이지 테이블을 사용하여 가상 주소 공간의 주소를 시스템의 실제 주소 공간에 있는 주소로 변환합니다. 각 PTE(페이지 테이블 항목)는 가상 메모리의 한 페이지를 실제 메모리 페이지에 매핑하므로 필요한 경우 페이징 작업이 발생합니다. MDL(메모리 설명자 목록)은 드라이버 DMA 작업과 연결된 버퍼에 대해 유사한 매핑을 제공합니다.

디바이스는 시스템의 전체 가상 주소 공간에 액세스하는 기능에 따라 다릅니다. 디바이스는 논리적(디바이스) 주소 공간에서 주소를 사용합니다. 각 HAL 은 맵 레지스터를 사용하여 디바이스 또는 논리 주소를 실제 주소(실제 RAM의 위치)로 변환합니다. 디바이스 하드웨어의 경우 맵 레지스터는 MDL(및 페이지 테이블)이 소프트웨어(드라이버)에 대해 수행하는 것과 동일한 기능을 수행합니다. 주소를 실제 메모리로 변환합니다.

이러한 주소 공간은 별도로 주소가 지정되므로 드라이버는 가상 주소 공간의 포인터를 사용하여 실제 메모리의 위치를 처리할 수 없으며 그 반대의 경우도 마찬가지입니다. 드라이버는 먼저 가상 주소를 실제 주소로 변환해야 합니다. 마찬가지로 디바이스는 논리 주소를 사용하여 실제 메모리에 직접 액세스할 수 없습니다. 디바이스는 먼저 주소를 변환해야 합니다.

HAL은 다양한 DMA 디바이스에 대해 DMA를 지원하는 어댑터 개체와 다른 컴퓨터의 I/O 버스를 설정해야 합니다. 예를 들어 대부분의 ISA DMA 컨트롤러, 하위 디바이스 및 버스 master 디바이스에는 32비트 프로세서의 전체 4기가바이트 시스템 물리적 주소 공간(또는 36비트 PAE 모드에서 실행되는 x86 프로세서의 64기가바이트 시스템 실제 주소)에 액세스할 수 있는 주소 줄이 부족합니다. 반면, PCI DMA 디바이스에는 일반적으로 32비트 프로세서의 전체 시스템 실제 주소 공간에 액세스할 수 있는 주소 줄이 충분합니다. 따라서 모든 HAL은 DMA 디바이스가 액세스할 수 있는 논리적 주소 범위와 각 컴퓨터의 실제 주소 범위 간에 매핑을 제공합니다.

각 어댑터 개체는 전송할 데이터의 양과 사용 가능한 메모리 양에 따라 하나 이상의 맵 레지스터와 연결됩니다. DMA 전송 중에 HAL은 각 맵 레지스터를 사용하여 디바이스에 액세스할 수 있는 논리 페이지를 CPU의 실제 메모리 페이지에 별칭을 지정합니다. 실제로 지도 레지스터는 디바이스에 분산/수집 기능이 있는지 여부에 관계없이 DMA를 사용하는 드라이버에 대한 분산/수집 지원을 제공합니다.

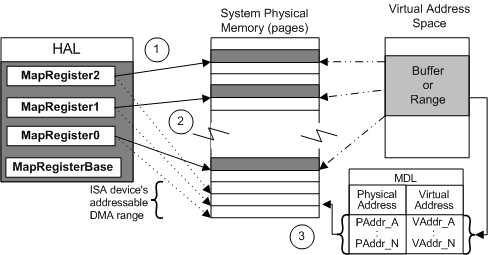

다음 그림에서는 분산/수집 기능이 없는 ISA DMA 디바이스의 드라이버에 대한 물리적-논리적 주소 매핑을 보여 줍니다.

이전 그림에서는 다음과 같은 유형의 매핑을 보여 줍니다.

각 맵 레지스터는 ISA DMA 디바이스의 하위 논리 주소(점선)에 다양한 물리적 주소(실선으로 가리키기)를 매핑합니다.

여기서 3개의 맵 레지스터는 시스템 실제 메모리의 세 페이징된 데이터 범위를 ISA DMA 디바이스에 대한 세 페이지 크기의 하위 논리 주소 범위에 별칭을 지정하는 데 사용됩니다.

ISA 디바이스는 매핑된 논리 주소를 사용하여 DMA 작업 중에 시스템 메모리에 액세스합니다.

비교 가능한 PCI DMA 디바이스의 경우 세 개의 페이지 크기 데이터 범위에 3개의 지도 레지스터도 사용됩니다. 그러나 매핑된 논리 주소 범위가 해당 물리적 주소 범위와 반드시 동일하지는 않으므로 PCI 디바이스도 논리 주소를 사용하여 시스템 메모리에 액세스합니다.

MDL의 각 항목은 가상 주소 공간의 위치를 실제 주소에 매핑합니다.

MDL의 맵 레지스터와 가상-물리적 항목 간의 대응에 유의하세요.

각 맵 레지스터 및 MDL의 각 가상 항목은 DMA 전송 작업에 대한 데이터의 전체 실제 페이지를 매핑합니다.

각 맵 레지스터 및 MDL의 각 가상 항목은 전체 데이터 페이지보다 작을 수 있습니다. 예를 들어 MDL의 초기 가상 항목은 물리적, 논리적 및 가상 주소 매핑 그림의 앞부분에서와 같이 실제 페이지 경계의 오프셋에 매핑될 수 있습니다.

각 맵 레지스터 및 MDL 맵의 각 가상 항목은 최소 1 바이트입니다.

읽기 또는 쓰기 작업을 요청하는 IRP에서 Irp-MdlAddress>의 불투명 드라이버 MDL의 각 가상 항목은 사용자 버퍼에 대한 시스템 실제 메모리의 페이지 경계를 나타냅니다. 마찬가지로, 단일 DMA 전송에 필요한 각 추가 맵 레지스터는 시스템 실제 메모리에 별칭이 지정된 디바이스 액세스 가능한 논리 주소 범위의 페이지 경계를 나타냅니다.

모든 Windows 플랫폼에서 각 어댑터 개체에는 플랫폼별(및 불투명-드라이버) 기본 주소에 있는 하나 이상의 맵 레지스터 집합이 연결되어 있습니다. 드라이버의 관점에서 볼 때, 샘플 ISA DMA 디바이스에 대한 주소 매핑을 보여 주는 그림에 표시된 지도 레지스터 기반은 칩, 시스템 DMA 컨트롤러 또는 버스 master 어댑터의 하드웨어 레지스터이거나 시스템 메모리에서 HAL에서 만든 가상 레지스터일 수 있는 맵 레지스터 집합에 대한 핸들입니다.

어댑터 개체에서 사용할 수 있는 맵 레지스터 수는 여러 디바이스 및 Windows 플랫폼에 따라 달라질 수 있습니다. 예를 들어 HAL은 다른 Windows 플랫폼의 DMA 컨트롤러에 다른 기능이 있기 때문에 일부 플랫폼에서 시스템 DMA를 사용하는 드라이버가 다른 플랫폼보다 더 많은 맵 레지스터를 사용할 수 있도록 할 수 있습니다.