レジスターのマッピング

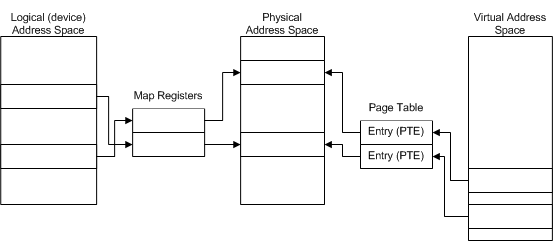

DMA を実行するドライバーでは、次の図に示すように 3 種類のアドレス空間を使用します。

どの Windows プラットフォームでも、プロセッサでサポートされている仮想アドレス空間全体にドライバーがアクセスできます。 32 ビット プロセッサでは、仮想アドレス空間は 4 ギガバイトに相当します。 CPU は、ページ テーブルを使用して、仮想アドレス空間でのアドレスをシステムの物理アドレス空間でのアドレスに変換します。 ページ テーブル エントリ (PTE) ごとに、仮想メモリの 1 ページが物理メモリのページにマッピングされ、必要に応じてページング操作が実行されます。 MDL (メモリ記述子リスト) は、ドライバーによる DMA 操作に関連付けられたバッファーに対して同様のマッピングを提供します。

デバイスからシステムの仮想アドレス空間全体にアクセスできるかどうかは、デバイスによって異なります。 デバイスで使用するアドレスは、論理 (デバイス) アドレス空間でのアドレスです。 各 HAL では、マップ レジスタを使用してデバイスのアドレス (論理アドレス) を物理アドレス (物理 RAM での場所) に変換します。 デバイスのハードウェアでは、MDL (およびページ テーブル) でソフトウェア (ドライバー) に対して実行される機能がマップ レジスタによって実行されます。これらの機能では、アドレスが物理メモリに変換されます。

これらのアドレス空間は互いに独立してアドレス指定されることから、ドライバーでは、仮想アドレス空間のポインターを使用して物理メモリの場所をアドレス指定できず、物理空間のポインターを使用して仮想メモリの場所をアドレス指定することもできません。 ドライバーでは、まず仮想アドレスを物理アドレスに変換する必要があります。 同様に、デバイスから論理アドレスを使用して物理メモリに直接アクセスすることはできません。 デバイスでは、まずアドレスを変換する必要があります。

HAL は、さまざまなコンピューター上で各種の DMA デバイスと I/O バスの DMA をサポートするアダプター オブジェクトを設定する必要があります。 たとえば、ほとんどの ISA DMA コントローラー、下位デバイス、バス マスター デバイスが扱うアドレス行は、32 ビット プロセッサが扱う 4 ギガバイトのシステム物理アドレス空間全体 (または 36 ビット PAE モードの x86 プロセッサが扱う 64 ギガバイトのシステム物理アドレス全体) にアクセスするには不十分です。 これに対し、PCI DMA デバイスには、32 ビット プロセッサのシステム物理アドレス空間全体にアクセスするうえで十分な数のアドレス行があることが普通です。 したがって、すべての HAL は、DMA デバイスがアクセスできる論理アドレス範囲とコンピューターごとの物理アドレス範囲との間でマッピングを提供します。

各アダプター オブジェクトは、転送データの量と使用可能なメモリの量に応じて、1 つ以上のマップ レジスタに関連付けられます。 DMA 転送中、HAL は各マップ レジスタを使用して、CPU の物理メモリのページに対応するように、デバイスからアクセス可能な論理ページのエイリアスを作成します。 実際には、デバイスにスキャッター/ギャザー機能があるかどうかに関係なく、DMA を使用するドライバーにはマップ レジスタからスキャッター/ギャザーのサポートが提供されます。

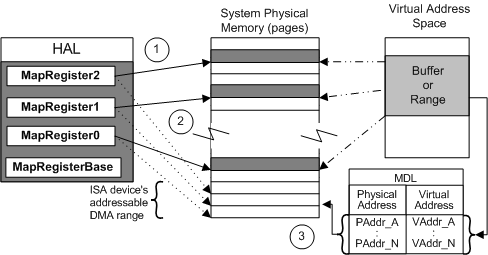

次の図は、スキャッター/ギャザー機能を持たない ISA DMA デバイスのドライバーに用意された、このような物理アドレスから論理アドレスへのマッピングを示しています。

前出の図は、次の種類のマッピングを示しています。

各マップ レジスタは、物理アドレスの範囲 (実線で示した範囲) を ISA DMA デバイスの下位論理アドレス (点線で示した範囲) にマッピングします。

ここでは、3 つのマップ レジスタを使用して、システム物理メモリの 3 つのページ範囲にあるデータに対して、ISA DMA デバイスの 3 ページ サイズの下位論理アドレス範囲に対応するエイリアスを作成します。

この ISA デバイスは、マッピングされた論理アドレスを使用して、DMA の操作でシステム メモリにアクセスします。

同等の PCI DMA デバイスの場合でも、3 つのページ サイズのデータ範囲に対応して 3 つのマップ レジスタが使用されます。 ただし、マッピングされた論理アドレス範囲が、それに対応する物理アドレス範囲と必ず同一であるとは限らないことから、PCI デバイスでは論理アドレスも使用してシステム メモリにアクセスします。

MDL の各エントリは、仮想アドレス空間の場所を物理アドレスにマッピングします。

マップ レジスタと MDL にある物理対仮想のエントリとの対応では、以下の点に注意してください。

各マップ レジスタと MDL の各仮想エントリは、DMA 転送操作のために最大で全物理ページのデータをマッピングします。

各マップ レジスタと MDL の各仮想エントリは、全ページのデータに満たない量のデータをマッピングできます。 たとえば、MDL の先頭にある仮想エントリを、前出の物理アドレス空間、論理アドレス空間、および仮想アドレス空間でのマッピングの図にあるように、物理ページ境界からのオフセットにマッピングできます。

各マップ レジスタと MDL の各仮想エントリは、少なくとも 1 バイトをマッピングします。

読み取り操作または書き込み操作を要求する IRP では、Irp->MdlAddress でドライバーに対して不透明な MDL にある各仮想エントリは、ユーザー バッファーに使用されているシステム物理メモリのページ境界を表します。 同様に、1 回の DMA 転送に必要な追加の各マップ レジスタは、デバイスからアクセス可能で、システムの物理メモリに対応するエイリアスを持つ論理アドレス範囲のページ境界を表します。

どの Windows プラットフォームでも、そのプラットフォームに固有でドライバーに対して不透明なベース アドレスにある 1 つ以上のマップ レジスタのセットが、各アダプター オブジェクトに関連付けられています。 ドライバーの観点から見ると、サンプル ISA DMA デバイスのアドレス マッピングの図にあるマップ レジスタのベースは、複数のマップ レジスタのセットに対するハンドルです。このマップ レジスタとして、チップ内部のハードウェア レジスタ、システム DMA コントローラー内部のハードウェア レジスタ、バス マスター アダプター内部のハードウェア レジスタ、システム メモリに HAL で作成した仮想レジスタなどが考えられます。

アダプター オブジェクトで使用できるマップ レジスタの数は、デバイスや Windows プラットフォームによって異なります。 たとえば、プラットフォームによっては、システム DMA を使用するドライバーに対して他のプラットフォームよりも多くのマップ レジスタを HAL で用意できます。この理由は DMA コントローラーの機能が Windows プラットフォームによって異なることにあります。