Préparez le matériel pour la veille moderne

Lors de l'entrée en veille moderne, les composants matériels doivent être prêts à effectuer la transition vers un fonctionnement à faible consommation d'énergie. Une fois que les composants logiciels et les applications ont été préparés pour un fonctionnement à faible consommation d'énergie, les composants matériels, y compris leurs pilotes de périphériques logiciels, doivent être préparés de la même manière pour un fonctionnement à faible consommation d'énergie.

Le reste de cet article explique comment préparer les périphériques à l'extérieur et à l'intérieur du système sur puce (SoC) pour qu'ils fonctionnent en mode basse consommation après la mise en veille de la plate-forme matérielle.

Transition matérielle en mode basse consommation

Tous les appareils en dehors du SoC et à l’intérieur du SoC doivent passer en mode basse consommation afin d’obtenir une longue durée de vie de la batterie pendant la veille. Une fois qu'une plateforme matérielle est entrée en veille, les appareils de la plateforme passent en mode basse consommation dans un processus ordonné qui commence par les appareils en dehors du SoC.

Tout d'abord, tous les périphériques en dehors du SoC ou du silicium central doivent passer en mode basse consommation. Le mode d'alimentation peut être un état d'inactivité dépendant de l'horloge, par exemple, placer un contrôleur tactile connecté à I²C en mode veille. Ou bien, le mode d'alimentation peut être un état de 0 watt à alimentation contrôlée appelé D3cold. Une caméra Web connectée par USB passera souvent à D3cold pendant la veille moderne. Pour plus d’informations, consultez Prise en charge de D3cold pour les périphériques USB.

Chaque classe de périphérique et bus de connexion a sa propre terminologie et ses propres exigences pour la transition d'un périphérique vers le mode de consommation la plus faible. Cependant, il est essentiel qu'un concepteur de système planifie un mode de fonctionnement à faible consommation d'énergie pour chaque appareil de la plateforme pendant la veille moderne. La durée de vie de la batterie du système et la possibilité de placer le SoC lui-même en mode basse consommation dépendent de la gestion correcte de l'alimentation de chaque appareil en dehors du SoC lui-même.

Ensuite, les périphériques réseau et radio sont placés en mode basse consommation pour la mise en veille. Pendant la mise en veille, ces appareils ont souvent encore de l’alimentation appliquée pour maintenir la connectivité et sont nécessaires pour réveiller le SoC si nécessaire. Les appareils de communication et de radio entrent généralement dans l’état de faible consommation D2/D3, bien que l’entrée dans chaque état soit propre à la classe d’appareil et spécifique au bus.

Une fois que tous les appareils en dehors du SoC, y compris les appareils de communication, ont été mis hors tension, les contrôleurs hôtes du SoC sont désactivés. Presque tous les SoC ont des contrôleurs hôtes USB, I²C, GPIO, SDIO et UART. Chacun de ces composants du SoC doit être désactivé pour que le SoC passe en mode basse consommation.

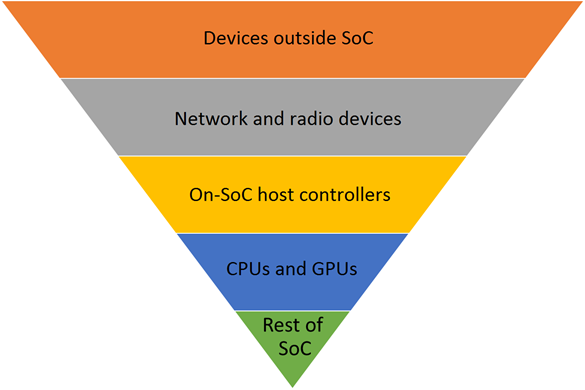

Le processus de préparation du matériel pour une faible consommation d’énergie pendant la mise en veille peut être visualisées sous la forme d’une pyramide à l’envers, comme illustré dans le diagramme suivant. La puissance la plus faible est atteinte lorsque toute la puce SoC est hors tension, mais cela ne peut se produire qu’après que chaque ensemble d’appareils au-dessus de celle-ci dans la pyramide a été mis hors tension.

Éteindre les appareils en dehors du SoC

Chaque appareil en dehors de la puce SoC doit entrer en mode basse consommation pour deux objectifs clés :

- Réduire la consommation électrique du périphérique.

- Autorisez le SoC lui-même à s'éteindre en autorisant le contrôleur hôte sur SoC, auquel le périphérique est connecté, à s'éteindre.

La méthode de mise hors tension de chaque périphérique en dehors du SoC varie selon la classe de périphérique et le bus connecté.

Certains appareils en dehors du SoC sont placés dans un état de 0 watt sans consommation d’énergie appelé D3cold. Les appareils courants pour D3cold incluent les caméras et les capteurs. Le pilote doit enregistrer l'état du registre du périphérique, puis faire passer le périphérique à l'état d'alimentation D3. L’alimentation est supprimée par le microprogramme ACPI en désactivant une ligne GPIO ou en désactivant une barre d’alimentation du circuit de gestion de l’alimentation (PMIC).

Certains appareils en dehors du SoC sont placés dans un mode d’inactivité à faible consommation dans lequel l’état d’enregistrement est maintenu, ou l’appareil peut simplement être fermé par horloge. Par exemple, de nombreux contrôleurs tactiles disposent d'un état d'horloge qui consomme moins de 1 milliwatt d'énergie. Les avantages typiques de l’utilisation d’un état fermé par horloge sont un temps d’alimentation plus rapide et un coût inférieur en n’ayant pas à connecter l’appareil à une barre d’alimentation commutable.

En règle générale, chaque appareil en dehors du SoC doit être capable d’entrer dans un mode basse consommation d’énergie qui consomme moins de 1 milliwatt d’énergie. Les appareils qui ne peuvent pas atteindre ce niveau d’alimentation avec un état d’horloge interne doivent implémenter la gestion de l’alimentation via D3cold.

Les appareils réseau et radio sont l'exception notable à la ligne directrice de 1 milliwatt. Les périphériques réseau et radio peuvent nécessiter plus de puissance pour maintenir une connexion au réseau ou pour écouter les périphériques sans fil. Certains concepteurs de système appellent ces transitions d’état d’alimentation runtime D3 (RTD3).

Gestion de l'alimentation dirigée pour les périphériques PCIe

Les cartes PCIe en dehors du SoC doivent activer un mécanisme de gestion de l'alimentation dirigée appelé Device-S4 afin de s'assurer qu'elles peuvent entrer en mode basse consommation. Sans Device-S4, si un utilisateur branche un périphérique sur un port racine PCIe avec des emplacements accessibles par l'utilisateur sur un système de veille moderne de bureau et que le pilote du périphérique ne prend pas en charge le runtime D3 (RTD3), le périphérique PCIe peut empêcher le système d'entrer dans DRIPS. Pour éviter ce problème, les OEM doivent opter pour les ports racine du périphérique PCIe vers Device-S4. Pour que Device-S4 soit activé pour un périphérique PCIe donné, les conditions suivantes doivent être remplies :

- Le port racine PCIe parent du périphérique doit être spécifié en tant que contrainte pour DRIPS.

- Le port racine PCIe parent doit appliquer la réinitialisation fondamentale du périphérique pour tous les enfants en aval du port racine lors de la transition D0->D3 du port racine et désactiver la réinitialisation fondamentale du périphérique pour ces enfants lors de la transition D3->D0. Pour plus d’informations sur les réinitialisations fondamentales de PCIe, reportez-vous à la section 6.6.1 de la spécification de base PCI Express. L’application de la réinitialisation fondamentale peut être fournie par des mécanismes ACPI supplémentaires. Pour plus d'informations, veuillez consulter ce guide sur la gestion de l'alimentation PCI. Pour indiquer que la plateforme respecte cette exigence de réinitialisation fondamentale, le microprogramme doit définir _DSD avec prise en charge du GUID {FDF06FAD-F744-4451-BB64-ECD792215B10}. Sans cela, le DRIPS dirigé ne sera pas déclenché pour les périphériques sous ce port racine PCIe. Pour plus d'informations, reportez-vous aux données spécifiques au périphérique ACPI (_DSD) pour les ports racine PCIe.

- Les ressources d’alimentation doivent être uniques à un port racine PCIe donné, c’est-à-dire ne pas être partagées avec un autre port racine.

Veuillez noter que les cartes PCIe qui nécessitent des modules de support de compatibilité (CSM) ne fonctionneront pas dans les systèmes de veille modernes. CSM n’est pas pris en charge dans le BIOS sur les systèmes de veille modernes en raison de l’exigence de démarrage sécurisé UEFI. Pour plus d'informations, reportez-vous à la spécification du programme de compatibilité matérielle de Windows.

Pour plus d'informations sur la gestion de l'alimentation pour des classes d'appareils particulières, les concepteurs de systèmes sont encouragés à consulter la gestion de l'alimentation spécifique au périphérique pour la veille moderne, ainsi que la documentation spécifique au périphérique sur Microsoft Collaborate.

Mise hors tension des périphériques réseau

La mise hors tension des périphériques réseau et radio est un autre élément clé de la préparation du matériel pour un fonctionnement à faible consommation pendant la mise en veille. Les appareils réseau et radio sont différents des autres appareils en dehors du SoC car ils doivent rester sous tension avec l'alimentation appliquée pour écouter les événements intéressants et réveiller le SoC. Par exemple, la radio Wi-Fi doit être capable d'écouter les paquets qui correspondent aux modèles WoL et de réveiller le SoC lorsqu'un paquet correspondant est détecté.

Windows fait passer les périphériques réseau à l'état D2/D3 pendant la veille s'ils sont censés réveiller le SoC. La pile réseau Windows configurera les modèles WoL et les déchargements de protocole avant de placer l'appareil dans l'état D2/D3 à faible consommation. Tous les périphériques réseau, y compris le Wi-Fi, le haut débit mobile (MBB) et l'Ethernet filaire, doivent être capables d'entrer dans l'état D2/D3 pendant la mise en veille. Si un périphérique réseau n’est pas nécessaire pour mettre en éveil le système, Windows fait passer l’appareil à l’état D3. Le périphérique réseau peut être placé dans l'état D3 si l'utilisateur a activé le mode avion ou désactivé le périphérique réseau spécifique.

Chaque appareil a une méthode physique différente pour réveiller le SoC de son mode de consommation le plus faible. Les périphériques réseau sur SDIO ou UART doivent signaler une ligne GPIO pour réveiller le SoC. Les périphériques réseau connectés via USB ou HSIC doivent utiliser la signalisation de reprise USB intrabande pour réveiller le SoC. Les périphériques réseau sur bus PCI ou PCIe doivent utiliser la signalisation PME intrabande pour réveiller le SoC.

En outre, un périphérique radio, tel qu’un périphérique Bluetooth ou un périphérique de communication en champ proche (NFC), est censé passer à l’état D2 si l’utilisateur a activé la radio pour cet appareil. À l’état D2, une radio Bluetooth écoute les événements d’entrée de souris et de claviers jumelés. Si un événement d'entrée est détecté, la radio Bluetooth bascule une ligne GPIO connectée au SoC, ce qui provoque la sortie du SoC de son mode basse consommation.

Chaque périphérique réseau ou radio a sa propre implémentation de mise hors tension pour une veille moderne. Les concepteurs de systèmes sont encouragés à lire les documents spécifiques aux classes d'appareils sur le site Web Microsoft Collaborate.

Mise hors tension des contrôleurs hôtes sur SoC

Une fois que tous les périphériques extérieurs au SoC, y compris les périphériques réseau et radio, ont été mis hors tension, les contrôleurs hôtes auxquels les périphériques sont connectés doivent s'éteindre. Les contrôleurs hôtes courants incluent USB, PCI, SDIO, GPIO et I²C.

Le pilote de chaque contrôleur hôte ne peut mettre le matériel hors tension qu'après la mise hors tension de chaque périphérique connecté au contrôleur hôte. Un exemple courant est le contrôleur hôte USB. Le contrôleur hôte USB ne peut s'éteindre qu'après que tous les périphériques USB qui lui sont connectés sont entrés dans un état de suspension sélective. Si un contrôleur hôte USB dispose d'une souris et d'un clavier USB connectés, le contrôleur hôte ne peut s'éteindre qu'une fois la souris et le clavier éteints. Si la souris ou le clavier reste sous tension, le contrôleur hôte USB reste également sous tension.

Tous les contrôleurs hôtes sur le SoC doivent être mis hors tension pour que le SoC lui-même s'éteigne. C’est pourquoi il est essentiel que chaque appareil effectue la gestion de l’alimentation des appareils. Le SoC lui-même ne peut s’éteindre que lorsque chaque contrôleur hôte est hors tension. Les contrôleurs hôtes ne peuvent être mis hors tension qu’une fois que tous les appareils qui leur sont connectés ont été mis hors tension.

Mise hors tension des processeurs et des GPU

En termes de gestion de l'alimentation, les processeurs et les GPU de la puce SoC sont différents des autres appareils. Les processeurs et les GPU s'éteignent dans le cadre de la mise hors tension du SoC lui-même et peuvent être éteints chaque fois qu'aucune activité logicielle ne leur est destinée.

La plupart des activités logicielles sur le système seront arrêtées au cours des étapes de préparation détaillées dans Préparer le logiciel pour la veille moderne. Les applications du Microsoft Store seront suspendues dans le cadre de la phase PLM. Les applications de bureau seront suspendues dans le cadre de la fin de la phase DAM. Les seules activités du processeur qui restent après que la plateforme entre dans la phase de résilience sont les opérations inactives de Windows lui-même. De même, il y a peu d'activité GPU car toutes les applications ont été mises en pause et l'écran est éteint.

Windows gère en permanence l'état d'alimentation des processeurs du système, même lorsque l'écran est allumé et que l'utilisateur travaille avec le PC. La même gestion de l’état de l’alimentation du processeur place les processeurs en mode basse consommation pendant la mise en veille. Lorsque tous les processeurs sont en mode basse consommation et que tous les contrôleurs hôtes du SoC ont été mis hors tension, le SoC lui-même peut être mis hors tension.

Mise hors tension du SoC

Lorsque tous les contrôleurs hôtes individuels, les processeurs et les GPU du SoC ont été mis hors tension, Windows détermine s’il est sûr de mettre hors tension l’ensemble du SoC lui-même. Le fournisseur de SoC fournit un plug-in de moteur d’alimentation (PEP) pour indiquer à Windows quand tout l’état du SoC a été enregistré afin que le SoC soit prêt à passer en mode basse consommation. Pour les SoC basés sur Intel, le PEP est fourni dans la boîte de réception.

Chaque fournisseur de SoC a une implémentation différente d’un état de faible consommation à l’échelle du SoC. Ces états sont généralement des états d’horloge ou d’alimentation dans lesquels le contenu de la mémoire est conservé lors de l’auto-actualisation et le système peut être réveillé par un minuteur programmable et un petit nombre de broches GPIO qui consomment très peu d’énergie. Windows fait référence à l’état d’alimentation du SoC le plus bas en tant qu’état de plateforme inactive du runtime le plus profond (DRIPS).

L’état DRIPS présente toujours les caractéristiques suivantes :

- DRIPS est l’état de consommation d’énergie le plus faible pour le SoC dans lequel la mémoire est conservée en mode d’actualisation automatique.

- DRIPS permet au SoC de se réveiller sur des événements provenant du réseau, de la radio et des périphériques d’entrée.

- Aucun code d’UC n’est autorisé à s’exécuter pendant l’état DRIPS.

- Lorsque le SoC est à l’état DRIPS, la plateforme consomme le moins d’énergie possible pendant la mise en veille (à l'exception des variations de consommation d'énergie causées par les périphériques réseau et radio).