Panel de estado

El panel Estado muestra expresiones booleanas para los valores de las variables del controlador, el modelo del sistema operativo y la regla. SDV usa estas expresiones para construir una abstracción del controlador, el modelo de sistema operativo y la regla, y las usa en la comprobación.

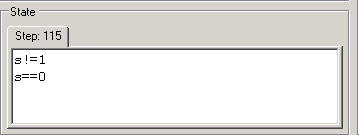

En la captura de pantalla siguiente se muestra un panel estado de ejemplo en el Visor de defectos.

El panel Estado es un componente del Visor de defectos. Cuando se resalta un elemento de código en el panel Árbol de seguimiento y la línea de código fuente correspondiente se resalta en el panel Código fuente, el panel Estado muestra las expresiones booleanas (del conjunto de expresiones que SDV realiza el seguimiento del controlador) que se evalúan como TRUE antes de que se ejecute la línea de código.

Seguimiento de expresiones booleanas

Al comprobar cada regla para el controlador, SDV realiza un seguimiento de un conjunto de expresiones booleanas. Las expresiones booleanas que se muestran en el panel Estado son las expresiones de ese conjunto que se evalúan como TRUE. Si el elemento del panel Árbol de seguimiento cambia el valor de cualquier expresión, el contenido del panel Estado cambia para mostrar el nuevo conjunto de expresiones que se evalúan como TRUE.

Interpretación de expresiones en el panel de estado

La mayoría de las expresiones que aparecen en el panel Estado están relacionadas con variables que son evidentes en el código de regla. Puede usar el código fuente de la regla (en el archivo RuleName.slic del panel Código fuente ) para ayudarle a interpretar las expresiones.

Sin embargo, algunas expresiones aparecen en el panel Estado sin detalles sobre su representación interna que puede ayudarle a interpretarlas. Por ejemplo,

x!=x

Para SDV, esta expresión representa una condición en la que el valor de la variable x en este punto del seguimiento no es igual al valor de la misma variable en un punto diferente del seguimiento. Use el código fuente del controlador, el código de regla (*.slic) y los elementos del panel Árbol de seguimiento para ayudarle a interpretar las expresiones.

Pestañas de paso en el panel de estado

Las expresiones booleanas del panel Estado se muestran en pestañas. Cada pestaña representa un paso del seguimiento a través de todo el código fuente utilizado en la comprobación. El número de la pestaña paso representa el orden de ese paso en el seguimiento.

Normalmente, dado que cada línea de código fuente representa solo un paso del seguimiento, solo habrá una pestaña de paso en el panel Estado . Sin embargo, el código complejo puede generar muchos pasos.

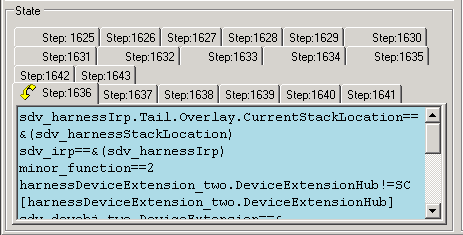

Por ejemplo, en la siguiente captura de pantalla se muestra el panel Estado que muestra una línea de código que incluye un puntero de función. En este caso, cada pestaña de paso representa un paso en la resolución del puntero, la llamada de la función a la que apunta y su resultado. (El número de pestañas de pasos muestra cuántos pasos se deben seguir para que SDV resuelva el puntero de función).

Para ver cada pestaña de paso en el panel Estado , seleccione la línea de código asociada en el panel Código fuente . A continuación, haga clic en la línea de código en el panel Código fuente repetidamente. Cada vez que haga clic en la línea de código seleccionada, SDV mostrará la pestaña de paso siguiente hasta que haya recorrido todas las pestañas de paso. La flecha amarilla curvada indica el paso seleccionado.

También puede hacer clic en cualquier pestaña del panel Estado para ver su contenido.

Comentario

A menudo, SDV realiza un seguimiento de las expresiones en el panel Estado que no aparecen en la regla y que no parecen estar directamente relacionadas con la regla. Estas expresiones resultan de una heurística sofisticada que SDV usa en sus intentos de correlacionar valores diferentes y infracciones de reglas diferentes. En algunas situaciones, SDV no puede evaluar correctamente la expresión. En estos casos, SDV proporciona un mensaje que indica que el estado actual es desconocido y muestra la expresión del paso con el último estado conocido. Consulte el ejemplo de código siguiente para obtener una explicación:

Unknown state. Last known state from step 120.

sdv irql current ==2

sdv irql current!=1

sdv irql current!=0