Requisitos de hardware para dispositivos WavePci

Al elegir las características de un nuevo diseño de hardware, los proveedores deben seguir estos principios generales:

En lugar de intentar simplemente mover todo el procesamiento al hardware, los proveedores deben pesar el costo de cada característica en contra de su impacto en el rendimiento.

Al considerar el valor potencial de una característica de hardware, un proveedor debe evaluar esa característica en términos de su impacto en el sistema en su conjunto en lugar de centrarse estrechamente en un subsistema determinado, como el audio.

Al seleccionar con criterio qué características acelerar en hardware, los proveedores pueden aliviar la carga de trabajo de CPU y mejorar el uso de memoria, lo que hace que haya más recursos del sistema disponibles para otras tareas.

Históricamente, no todos los diseños de hardware de audio se han realizado correctamente siguiendo estos principios.

Al reproducir contenido de audio o mezclar varias secuencias, algunos controladores de audio WDM consumen de forma innecesaria una gran cantidad de tiempo de CPU y ancho de banda de bus. Estas deficiencias suelen ser el resultado de diseños de hardware defectuosos e implementaciones de controladores ineficaces. Los defectos de diseño de hardware también pueden impedir que un controlador de audio controle determinados formatos de onda o requiera soluciones alternativas que requieran intervención de software.

El propósito del modelo de dispositivo WaveCíclico es adaptarse a las limitaciones de hardware de los dispositivos de audio más antiguos. Los nuevos diseños de hardware deben ser totalmente compatibles con WavePci.

Un dispositivo WavePci que puede realizar una dispersión o recopilación verdadera de DMA elimina la necesidad de que la CPU dedique tiempo a copiar datos de audio entre búferes. A diferencia de WaveCíclica, WavePci no tiene necesidad inherente de copiar datos, por lo que es el controlador de miniporte preferido para dispositivos de audio acelerados por hardware o multistream. Un dispositivo WavePci bien diseñado debe consumir casi sin recursos de CPU, lo que permite enviar un gran número de secuencias de audio (64 o más) al hardware para el procesamiento y la mezcla 3D.

Un dispositivo WavePci requiere un controlador DMA maestro de bus que admita transferencias DMA de dispersión y recopilación. Los diseños de hardware no deben colocar límites arbitrarios en los tipos de transferencias de datos que el controlador DMA puede controlar. Un dispositivo WavePci debe cumplir los siguientes requisitos:

El dispositivo debe ser un maestro de bus.

Debe poder acceder de forma autónoma a la memoria del sistema sin intervención del sistema operativo y sin usar recursos DMA del sistema.

El dispositivo debe poder controlar las transferencias de datos de longitud arbitraria.

Debe controlar las asignaciones (vea IPortWavePciStream::GetMapping) más grande que una página de memoria. Un dispositivo con una limitación de transferencia de 4 kilobytes, por ejemplo, no se ajusta a los requisitos completos de WavePci. En CPU de 64 bits que admiten Microsoft Windows, el tamaño de página es de 8 kilobytes, lo que hace que algunas asignaciones tengan un tamaño superior a 4 kilobytes. Las transferencias de datos que superan los 32 kilobytes de una sola asignación son teóricamente posibles, en función de la fragmentación de memoria física. En el otro extremo, es posible un tamaño de asignación de un byte.

El dispositivo debe controlar las transferencias de datos hacia o desde cualquier ubicación en la memoria del sistema.

Es muy probable que las transferencias de datos que se extienden entre 32 kilobytes o límites de potencia de dos más grandes. Un equipo ahora puede contener más de 4 gigabytes de RAM y, en esos sistemas, las asignaciones se pueden ubicar más de 4 gigabytes en memoria física en el caso de una CPU de 64 bits o la extensión de dirección física x86 (PAE). Para lograr el mejor rendimiento en estas máquinas, los proveedores deben crear dispositivos que admitan direccionamiento de 64 bits. De lo contrario, se requiere la copia de datos en software. Históricamente, la copia de datos ha sido necesaria para dispositivos con direccionamiento de 24 bits en sistemas con más de 16 megabytes de RAM. Los dispositivos deben usar WaveCíclica en lugar de WavePci si no pueden leer ni escribir en cualquier parte de la memoria física. Un controlador puede tomar esta decisión en el momento de inicio del dispositivo (consulte IRP_MN_START_DEVICE) después de haber tenido la oportunidad de determinar si su alcance de dirección es suficiente para acceder al intervalo de direcciones completo del bus de memoria del sistema.

El dispositivo debe controlar las transferencias de datos con alineación arbitraria.

Las asignaciones pueden comenzar y terminar en límites de bytes arbitrarios en la memoria. Un marco de datos de audio se puede dividir entre asignaciones, con las muestras de los primeros canales al final de la primera asignación y las muestras para los canales restantes en la segunda asignación. Para obtener un ejemplo, consulte Filtros de onda. Para algunos tamaños de ejemplo, incluso un contenedor de ejemplo se puede dividir entre asignaciones. Si el dispositivo requiere que las transferencias estén en los límites de la línea de caché, o si el dispositivo requiere que las transferencias estén estrictamente alineadas con los límites del marco de audio (por ejemplo, suponiendo que el tamaño de transferencia se divide uniformemente en cuatro, en el caso estéreo de 16 bits), este dispositivo no es adecuado para el cumplimiento completo de WavePci. Tenga en cuenta que un elemento de hardware no conforme se puede exponer como un dispositivo WavePci limitando los intervalos de datos o formatos que expone el controlador (por ejemplo, solo ciertas profundidades de bits o solo determinadas configuraciones de canal).

Con respecto al último punto de la lista anterior, el motor DMA de dispersión o recopilación de un dispositivo WavePci debe controlar los búferes que delimiten los límites de la página de memoria. Por ejemplo, un búfer que contiene 10 milisegundos por valor de muestras de audio PCM de 16 bits para un flujo de onda de 48 kHz, el flujo de onda de 5,1 canales tiene el siguiente tamaño:

(6 samples/frame)*(2 bytes/sample)*(48K frames/second)*(10 milisegundos) = 5760 bytes

Esto supera el tamaño de página de memoria (4096 bytes), lo que significa que el búfer contiene uno o dos límites de página, en función de cómo se coloca en la memoria. El búfer contiene un número entero (480) de fotogramas de datos de audio, pero uno o dos de estos fotogramas podrían estar entre límites de página.

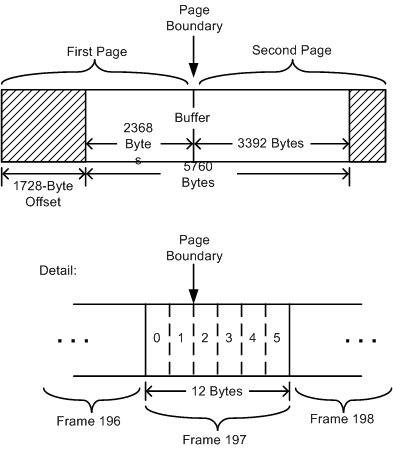

Por este motivo, el hardware DMA de dispersión y recopilación para un dispositivo WavePci debe diseñarse para controlar fotogramas de audio (como el marco 197 de la ilustración siguiente) que se dividen entre dos páginas físicamente no contiguas en memoria.

En la parte superior de la ilustración anterior se encuentra un búfer de 5760 bytes que separa el límite entre dos páginas. En este ejemplo, el búfer comienza en un desplazamiento de 1728 bytes desde el inicio de la primera página, que alinea el inicio del búfer con un límite de 64 bytes en memoria. Supongamos que cada fotograma de audio ocupa 12 bytes y contiene seis canales. La primera página contiene todos los fotogramas entre 0 y 196, pero solo los cuatro primeros bytes del marco 197.

En la parte inferior de la figura se muestra una vista detallada de la trama de audio 197, que muestra que solo las muestras de los canales 0 y 1 se encuentran dentro de la primera página. Las muestras de los canales del 2 al 5 se encuentran en la segunda página.

Aunque las dos páginas aparecen entre sí en la parte superior de la figura, son, de hecho, contiguos solo en la memoria virtual del kernel. Dado que las páginas que contienen el búfer no son contiguas en la memoria física, un controlador DMA de dispersión o recopilación, que usa direcciones físicas, debe especificar las dos partes del búfer como dos entradas independientes en su cola de transferencia. El controlador de puerto WavePci divide automáticamente el búfer en dos asignaciones físicas independientes en el límite de la página.

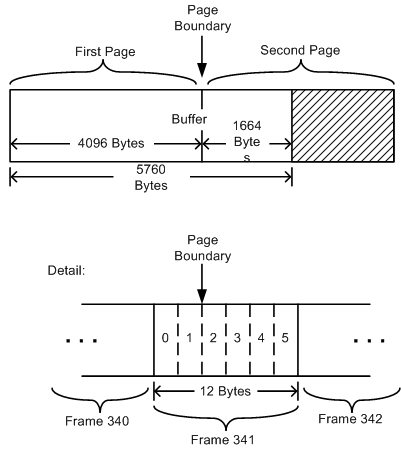

Incluso si se cambia el ejemplo anterior para alinear el búfer con el inicio de la primera página, el problema del marco dividido no desaparece. En la ilustración siguiente se muestra este punto. En este caso, el marco 341 se divide en el límite de la página con las muestras para los canales 0 y 1 de nuevo dentro de la primera página y las muestras de los canales del 2 al 5 ubicados en la segunda página.

Un dispositivo WavePci cuyo controlador DMA de dispersión y recopilación no controla correctamente fotogramas de audio divididos está limitado en los tipos de formatos de datos de audio que puede controlar, aunque las soluciones alternativas de software pueden ayudar a aliviar algunos defectos de diseño de hardware. Para obtener más información, consulte Latencia de WavePci.