RSS mit Hardware Queuing

RSS mit Hardwarewarteschlange verbessert die Systemleistung relativ zu RSS mit einer einzelnen Hardware-Empfangswarteschlangenlösung. NICs, die Hardwarewarteschlangen unterstützen, weisen empfangene Daten mehreren Empfangswarteschlangen zu. Die Empfangswarteschlangen sind einer CPU zugeordnet. Die NIC weist empfangene Daten cpUs basierend auf Hashwerten und einer Dereferenzierungstabelle zu.

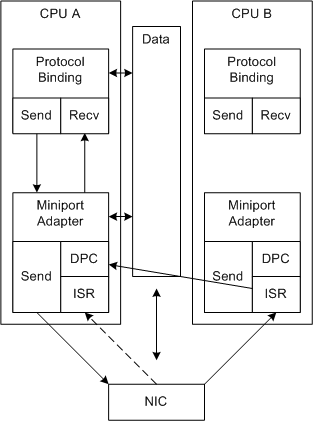

Die folgende Abbildung veranschaulicht RSS mit NIC-Empfangswarteschlange.

In der Abbildung stellen die gestrichelten Pfeile einen alternativen Pfad für die Empfangsverarbeitung dar. RSS kann die CPU, die den anfänglichen ISR-Aufruf empfängt, nicht steuern. Der Treiber muss die Daten nicht in die Warteschlange stellen, sodass er sofort die anfänglichen DPCs auf den richtigen CPUs planen kann.

Der folgende Prozess wird für jeden Interrupt wiederholt:

Die NIC:

Verwendet DMA, um Puffer mit empfangenen Daten zu füllen.

Der Miniporttreiber hat während der Initialisierung die Empfangspuffer im freigegebenen Speicher zugeordnet.

Berechnet einen Hashwert.

Stellt den Puffer für eine CPU in die Warteschlange und stellt die Warteschlangenzuweisungen für den Miniporttreiber bereit.

Beispielsweise könnte die NIC die Schritte 1 bis 3 und DMA eine Liste der CPU-Zuweisungen nach dem Empfang einer bestimmten Anzahl von Paketen durchschleifen. Der spezifische Mechanismus bleibt dem NIC-Entwurf überlassen.

Unterbricht das System.

Die empfangenen Puffer, die das System in einem Interrupt verarbeitet, werden auf die CPUs verteilt.

NDIS ruft die MiniportInterrupt-Funktion (ISR) des Miniporttreibers für eine systembestimmte CPU auf.

Der Miniporttreiber fordert NDIS auf, verzögerte Prozeduraufrufe (DpCs) für jeden der CPUs mit einer nicht leeren Warteschlange in die Warteschlange zu stellen.

Beachten Sie, dass alle DPCs abgeschlossen werden müssen, bevor der Treiber Unterbrechungen aktiviert. Beachten Sie auch, dass der ISR möglicherweise auf einer CPU ausgeführt wird, die keine Puffer zu verarbeiten hat.

NDIS ruft die MiniportInterruptDPC-Funktion für jeden DPC in der Warteschlange auf. Der DPC für eine bestimmte CPU:

Builds empfangen Deskriptoren für alle empfangenen Puffer in der Warteschlange und geben die Daten im Treiberstapel an.

Weitere Informationen finden Sie unter Angeben von RSS-Empfangsdaten.

Aktiviert die Interrupts, wenn es sich um den letzten DPC handelt, der abgeschlossen werden soll. Dieser Interrupt ist abgeschlossen, und der Prozess wird erneut gestartet. Der Treiber muss einen atomischen Vorgang verwenden, um den letzten DPC zu identifizieren, der abgeschlossen werden soll. Der Treiber kann beispielsweise die NdisInterlockedDecrement-Funktion verwenden, um einen atomischen Zähler zu implementieren.