Status der MT3620-Unterstützung

Wichtig

Dies ist die Dokumentation zu Azure Sphere (Legacy). Azure Sphere (Legacy) wird am 27. September 2027 eingestellt, und Benutzer müssen bis zu diesem Zeitpunkt zu Azure Sphere (integriert) migrieren. Verwenden Sie die Versionsauswahl oberhalb des Inhaltsverzeichniss, um die Dokumentation zu Azure Sphere (Integriert) anzuzeigen.

In diesem Dokument wird der aktuelle Status der Azure Sphere-Unterstützung für die MediaTek MT3620 beschrieben. Sie können auch auf den MT3620 Product Brief verweisen, der auf der MediaTek MT3620-Webseite zum Download zur Verfügung steht. Darüber hinaus produziert MediaTek das MT3620 Hardware User Guide, ein detaillierter Leitfaden zur Integration der MT3620 MCU in Ihre eigene Hardware.

Wichtig

Im Rahmen dieses Dokuments bedeutet derzeit nicht unterstützt, dass Verwendung der Funktion durch den Kunden zum aktuellen Zeitpunkt eingeschränkt ist, und dass diese Einschränkung in der Zukunft wahrscheinlich entfernt wird. Im Gegensatz dazu bedeutet kein Zugriff darauf, dass die Funktion nicht von Kunden verwendet werden kann, und dass diese Einschränkung wahrscheinlich nicht geändert wird.

Wenn Sie Featureanfragen oder Feedback haben, freuen wir uns über Ihre Kommentare im Azure Sphere-Communityforum.

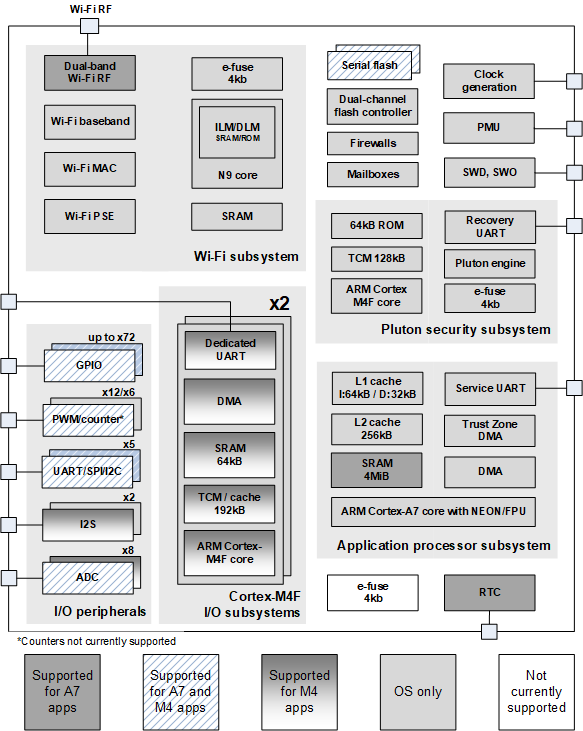

MT3620-Blockdiagramm

Das Blockdiagramm zeigt die Unterstützung für jede MT3620-Komponente. Die Abschnitte, die dem Diagramm folgen, enthalten zusätzliche Details zu diesen Komponenten.

E/A-Peripheriegeräte

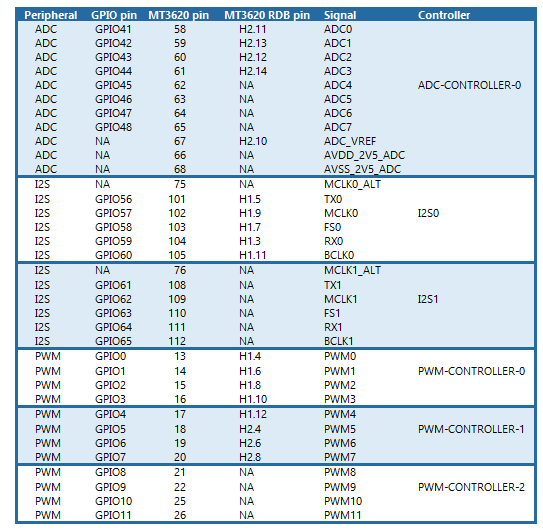

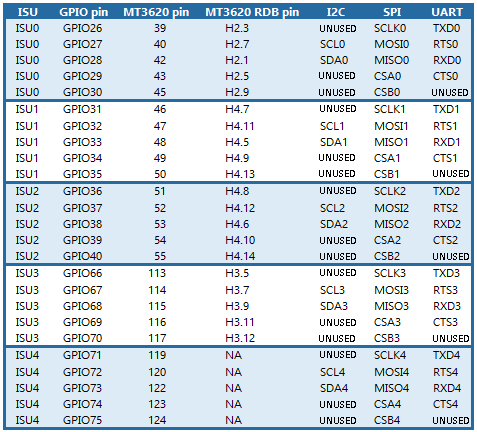

Das MT3620-Design umfasst insgesamt 76 programmierbare I/O-Pins. Wie in den folgenden beiden Tabellen gezeigt, werden die meisten Pins zwischen allgemeinem E/A (GPIO) und anderen Funktionen multixiert. Zusätzlich zu den aufgeführten GPIO-Pins sind GPIO12-23 auf MT3620 Pins 27-38 erhältlich.

In Bezug auf die folgende Tabelle werden Pins, die als "NICHT VERWENDET" gekennzeichnet sind, nicht vom zugehörigen ISU-Peripheriegerät verwendet und können für die Verwendung als GPIO-Pins konfiguriert werden.

Hinweis

Sobald ein ISU-Peripheriegerät einem Kern zugeordnet wurde, sind alle 5 ISU-Pins, einschließlich nicht verwendeter Pins, auf die Verwendung in diesem Kern beschränkt.

GPIO/PWM/Leistungsindikatoren

Einige Pins schalten im Multiplexbetrieb zwischen GPIO, Pulsbreitemodulation (Pulse Width Modulation) und Leistungsindikatoren für Hardware um.

Zurzeit unterstützte GPIO-Funktionen legen die Ausgabeeingabe hoch/niedrig und die Leseeingabe fest. Offene Entwässerungs-/Open-Source-Fahrmodi und die Steuerung der Antriebsfestigkeit werden ebenfalls unterstützt. Externe Interrupts werden auf dem M4-Kern, aber nicht auf dem A7-Kern unterstützt.

MT3620 verfügt über 12 PWM-Kanäle (PWM0 bis PWM11). Sie sind in drei Gruppen mit jeweils vier Kanälen organisiert. Jede Gruppe ist einem PWM-Controller zugeordnet (PWM-CONTROLLER-0, PWM-CONTROLLER-1, PWM-CONTROLLER-2). Die PWM-Kanäle und GPIO-Pins GPIO0 bis GPIO11 entsprechen denselben Pins auf dem MT3620. Wenn Ihre Anwendung einen PWM-Controller verwendet, werden alle pins, die diesem Controller zugeordnet sind, für die Verwendung als PWM-Ausgabe zugewiesen, und keine davon kann für GPIO verwendet werden.

Die PWM-Hardware kann für die Verwendung einer von drei Festtaktfrequenzen konfiguriert werden: 32 KHz, 2 MHz (XTAL/13) oder 26 MHz (XTAL). Auf den Rt-Kernen (Real-Time) kann eine Echtzeitanwendung (RTApp) auswählen, welche Uhr als Basis verwendet werden soll. Auf dem High-Level-Core (A7) verwendet der Linux-Treiber immer die 2 MHz Takt. Dies führt zu Leistungszyklen und Periodenbeschränkungen bei anwendungen auf hoher Ebene, wie in der Verwendung von PWMs in high-level-Anwendungen erläutert.

Serielle Schnittstellenblöcke (ISU)

Das Design des MT3620 umfasst fünf serielle Schnittstellenblöcke, von denen jeder fünf Pins aufweist. (Diese Blöcke werden auch als ISU bezeichnet, die Kurzform für „I2C, SPI, UART“.) Diese seriellen Schnittstellenblöcke können GPIO, UART (Universal Asynchronous Receiver-Transmitter), I2C (Inter-integrated Circuit) und serieller Peripherieschnittstelle (Serial Peripheral Interface, SPI) multiplexen.

UART wird bei 1.200, 2.400, 4.800, 9.600, 19.200, 38.400, 57.600, 115.200, 230.400, 460.800, 500.000, 576.000, 921.600, 1.000.000, 1.152.000, 1.500.000 und 2.000.000 Baud unterstützt. Es gibt einen 32-Byte-Hardwareempfangspuffer. Die folgenden UART-Einstellungen werden unterstützt, und 8N1 (8 Datenbits, 1 Stoppbit und keine Parität) ist die Standardeinstellung:

- Datenbit: 5, 6, 7 und 8.

- Stoppbit: 1 und 2.

- Parität: „Ungerade“, „Gerade“ und „Keine“.

- Ablaufsteuerungsmodus: RTS/CTS, XON/XOFF und keine Flusssteuerung.

SPI-Transaktionen mit bis zu 40 MHz werden unterstützt. Sie können pro ISU maximal zwei untergeordnete SPI-Geräte verbinden. Wenn Sie einen ISU-Port als SPI-Masterschnittstelle nutzen, können Sie nicht den gleichen Port wie für eine I2C- oder UART-Schnittstelle verwenden. Gleichzeitige bidirektionale SPI-Lese- und -Schreibvorgänge (Vollduplex) innerhalb einer Bustransaktion werden nicht unterstützt. Die folgenden SPI-Einstellungen werden unterstützt:

- Kommunikationsmodus (Uhr polarität, Uhrphase): SPI Mode 0 (CPOL = 0, CPHA = 0), SPI Mode 1 (CPOL = 0, CPHA = 1), SPI Mode 2 (CPOL = 1, CPHA = 0) und SPI Mode 3 (CPOL = 1, CPHA = 1).

- Bitreihenfolge: „Unwichtigstes Bit zuerst“ und „Wichtigstes Bit zuerst“.

- Chipauswahlpolarität: „Aktiv hoch“, „Aktiv niedrig“. „Aktiv niedrig“ ist die Standardeinstellung.

7-Bit-Adressen für untergeordnete Geräte werden für I2C unterstützt. 8-Bit- oder 10-Bit-I2C-Untergeordnete Adressen werden nicht unterstützt. Wenn Sie einen ISU-Port als I2C-Masterschnittstelle nutzen, können Sie nicht den gleichen Port wie für eine SPI- oder UART-Schnittstelle verwenden. I2C-Lesevorgänge mit 0 Byte werden nicht unterstützt. Die folgenden I2C-Einstellungen werden unterstützt:

- Busgeschwindigkeiten 100 KHz, 400 KHz und 1 MHz.

- Benutzerdefiniertes Zeitlimit für Vorgänge.

I2S

Zwei Blöcke mit fünf Pins betreiben Multiplexing zwischen GPIO und I2S. I2S wird derzeit nur für M4-Anwendungen unterstützt.

ADC

MT3620 enthält einen 12-Bit-ADC mit 8 Eingabekanälen. Ein Block von acht Pins wird zwischen GPIO und ADC multixiert. Die ADC-Eingabekanäle und die GPIO-Pins GPIO41 bis GPIO48 entsprechen denselben Pins auf dem MT3260. Wenn Ihre Anwendung jedoch den ADC verwendet, werden alle 8 Pins für die Verwendung als ADC-Eingaben zugewiesen, und keine davon kann für GPIO verwendet werden.

ARM Cortex-M4F-Subsysteme

Der MT3620 ist mit zwei ARM Cortex-M4F-Allzwecksubsystemen ausgestattet, von denen jedes über einen dedizierten GPIO/UART-Block verfügt.

Der MT3620 unterstützt eine Standardtaktrate von 26 MHz. Jeder M4-Kern kann aber separat so konfiguriert werden, dass eine beliebige Taktrate zwischen 1 MHz und 200 MHz verwendet wird, indem der HCLK_CK_CTRL-Registerwert festgelegt wird. Der folgende Code veranschaulicht eine Möglichkeit zum Festlegen der Taktrate auf 200 MHz:

volatile unsigned int *hclk_ck_ctrl = (unsigned int *)0x2101000c;

*hclk_ck_ctrl = 0x00040200;

Hinweis

Ausführliche Informationen zur Programmierung der M4-Kerne auf dem MT3620 finden Sie in der von MediaTek veröffentlichten MT3620-Dokumentation . Wenn das Datenblatt nicht alle Informationen enthält, die Sie benötigen, senden Sie eine E-Mail an Avnet (Azure.Sphere@avnet.com), um das vollständige Datenblatt anzufordern.

Die ARM Cortex-M4F Subsysteme können so programmiert werden, dass externe Unterbrechungen unterstützt werden. Weitere Informationen finden Sie unter Verwenden externer Interrupts in Echtzeit-fähigen Anwendungen .

Anwendungsprozessor-Subsystem

Das ARM Cortex-A7-Subsystem führt eine Kundenanwendung zusammen mit dem von Microsoft bereitgestellten Linux-basierten Kernel, Diensten und Bibliotheken aus.

Der UART-Dienst ist speziell für Systemfunktionen des A7-Subsystems reserviert. Er steht nicht zur Verwendung durch Kundenanwendungen zur Verfügung.

Der einmalig programmierbare e-fuse-Block zum Speichern von gerätespezifischen Informationen kann nicht für Kundenanwendungen verwendet werden.

WLAN-Subsystem

Das WLAN-Subsystem ist derzeit konform mit IEEE 802.11 b/g/n mit 2,4 GHz und 5 GHz.

Derzeit unterstützt Azure Sphere nur WPA2-, EAP-TLS- und open(no password)-Authentifizierung.

Informationen zu Hochfrequenztests und der zugehörigen Kalibrierung finden Sie unter Tools für Hochfrequenztests.

Stromversorgungssteuerung

Das MT3620 umfasst Power Down - und Power Profile-Funktionen , um den Stromverbrauch zu steuern. Ausführliche Informationen finden Sie unter Power Down-Überlegungen und Überlegungen zu Power Profile.

Uhren und Stromquellen

Der Hauptquarz kann derzeit nur 26 MHz sein. Andere Quarzfrequenzen als 26 MHz werden derzeit in der Software nicht unterstützt.

Spannungsabfallerkennung

Spannungsabfallerkennung wird derzeit nicht unterstützt.

Hardware-Watchdog-Timer

Die MTK3620 umfasst mehrere Watchdog-Timer:

- Ein Watchdog-Timer, der für die Verwendung durch die Pluton-Sicherheitsdomäne reserviert ist. Dieser Watchdog-Timer ist nicht für die Verwendung durch Anwendungen verfügbar.

- Ein Watchdog-Timer, der für den Anwendungsprozessor verfügbar ist. Das Azure Sphere-Betriebssystem verwendet diesen Watchdog-Timer für Systemdienste. Dieser Watchdog-Timer ist für Anwendungen nicht verfügbar.

- Ein Watchdog-Timer für jeden der Echtzeitkerne. Diese Watchdog-Timer sind für Echtzeitanwendungen verfügbar.

Weitere Informationen finden Sie unter Verwenden eines Watchdog-Timers in einer RTApp .

SWD, SWO

SWD (Serial-Wire Debug, Pins 98 - 99) wird nur für M4-Anwendungen unterstützt. Die Serielle Drahtausgabe (SWO, Pin 100) wird derzeit nicht unterstützt. Das Debuggen einer A7-Anwendung wird durch einen von Microsoft bereitgestellten GDB-basierten Mechanismus unterstützt.

RAM und Flashspeicher

Die MT3620-Einheit ist mit ca. 5 MB RAM On-Die, einschließlich 256 KiB in jedem E/A-Subsystem und 4 MB im A7-Anwendungssubsystem, ausgestattet.

Der MT3620 kann mit 16 MB SPI-Flashspeicher bestellt werden.

Informationen zum verfügbaren RAM und Flashspeicher für Anwendungen finden Sie unter Für Anwendungen verfügbarer Arbeitsspeicher.

Unterstützung für Fertigungsprüfung

Dokumentation und Hilfsprogramme zur Unterstützung der Integration von benutzerdefinierten Fertigungstestanwendungen in Produktionsanlagenprozesse sind noch nicht verfügbar.

Pinout

| Pin-Nr. | Pin-Name | Hauptfunktionen | Typ | Beschreibung | Kommentare |

|---|---|---|---|---|---|

| 1 | GND | P | Masse/Erde | ||

| 2 | AVDD_3V3_WF_A_PA | PI | 3,3 V-Stromversorgungsschiene für 5 GHz-WLAN-Leistungsverstärker | ||

| 3 | AVDD_3V3_WF_A_PA | PI | 3,3 V-Stromversorgungsschiene für 5 GHz-WLAN-Leistungsverstärker | ||

| 4 | NC | ||||

| 5 | NC | ||||

| 6 | AVDD_1V6_WF_TRX | PI | 1,6 V-Stromversorgungsschiene für WLAN-Übertragung/-Senden | ||

| 7 | AVDD_1V6_WF_AFE | PI | 1,6 V-Stromversorgungsschiene für analoges WLAN-Front-End | ||

| 8 | NC | ||||

| 9 | AVDD_1V6_XO | PI | 1,6 V-Stromversorgungsschiene für Hauptquarzoszillator | ||

| 10 | MAIN_XIN | KI | Hauptquarzoszillator-Eingang | ||

| 11 | WF_ANTSEL0 | DO | WLAN-Antennenauswahl für externen DPDT-Switch | ||

| 12 | WF_ANTSEL1 | DO | WLAN-Antennenauswahl für externen DPDT-Switch | ||

| 13 | GPIO0 | GPIO0/PWM0 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 14 | GPIO1 | GPIO1/PWM1 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 15 | GPIO2 | GPIO2/PWM2 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 16 | GPIO3 | GPIO3/PWM3 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 17 | GPIO4 | GPIO4/PWM4 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 18 | GPIO5 | GPIO5/PWM5 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 19 | GPIO6 | GPIO6/PWM6 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 20 | GPIO7 | GPIO7/PWM7 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 21 | GPIO8 | GPIO8/PWM8 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 22 | GPIO9 | GPIO9/PWM9 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 23 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 24 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 25 | GPIO10 | GPIO10/PWM10 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 26 | GPIO11 | GPIO11/PWM11 | DIO | Interrupt-fähige GPIO mit Multiplexing für PWM-Ausgabe | |

| 27 | GPIO12 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 28 | GPIO13 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 29 | GPIO14 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 30 | GPIO15 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 31 | GPIO16 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 32 | GPIO17 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 33 | GPIO18 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 34 | GPIO19 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 35 | GPIO20 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 36 | GPIO21 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 37 | GPIO22 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 38 | GPIO23 | DIO | Interrupt-fähige GPIO | Interrupts werden derzeit nicht unterstützt. | |

| 39 | GPIO26 | GPIO26/SCLK0/TXD0 | DIO | GPIO mit Multiplexing für ISU 0-Funktionen | |

| 40 | GPIO27 | GPIO27/MOSI0/RTS0/SCL0 | DIO | GPIO mit Multiplexing für ISU 0-Funktionen | |

| 41 | GND | P | Masse/Erde | ||

| 42 | GPIO28 | GPIO28/MISO0/RXD0/SDA0 | DIO | GPIO mit Multiplexing für ISU 0-Funktionen | |

| 43 | GPIO29 | GPIO29/CSA0/CTS0 | DIO | GPIO mit Multiplexing für ISU 0-Funktionen | |

| 44 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 45 | GPIO30 | GPIO30/CSB0 | DIO | GPIO mit Multiplexing für ISU 0-Funktionen | |

| 46 | GPIO31 | GPIO31/SCLK1/TXD1 | DIO | GPIO mit Multiplexing für ISU 1-Funktionen | |

| 47 | GPIO32 | GPIO32/MOSI1/RTS1/SCL1 | DIO | GPIO mit Multiplexing für ISU 1-Funktionen | |

| 48 | GPIO33 | GPIO33/MISO1/RXD1/SDA1 | DIO | GPIO mit Multiplexing für ISU 1-Funktionen | |

| 49 | GPIO34 | GPIO34/CSA1/CTS1 | DIO | GPIO mit Multiplexing für ISU 1-Funktionen | |

| 50 | GPIO35 | GPIO35/CSB1 | DIO | GPIO mit Multiplexing für ISU 1-Funktionen | |

| 51 | GPIO36 | GPIO36/SCLK2/TXD2 | DIO | GPIO mit Multiplexing für ISU 2-Funktionen | |

| 52 | GPIO37 | GPIO37/MOSI2/RTS2/SCL2 | DIO | GPIO mit Multiplexing für ISU 2-Funktionen | |

| 53 | GPIO38 | GPIO38/MISO2/RXD2/SDA2 | DIO | GPIO mit Multiplexing für ISU 2-Funktionen | |

| 54 | GPIO39 | GPIO39/CSA2/CTS2 | DIO | GPIO mit Multiplexing für ISU 2-Funktionen | |

| 55 | GPIO40 | GPIO40/CSB2 | DIO | GPIO mit Multiplexing für ISU 2-Funktionen | |

| 56 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 57 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 58 | GPIO41 | GPIO41/ADC0 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 59 | GPIO42 | GPIO42/ADC1 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 60 | GPIO43 | GPIO43/ADC2 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 61 | GPIO44 | GPIO44/ADC3 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 62 | GPIO45 | GPIO45/ADC4 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 63 | GPIO46 | GPIO46/ADC5 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 64 | GPIO47 | GPIO47/ADC6 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 65 | GPIO48 | GPIO48/ADC7 | DIO | GPIO mit Multiplexing für ADC-Eingang | |

| 66 | AVDD_2V5_ADC | PI | 2,5 V-Stromversorgungsschiene für ADC | ||

| 67 | VREF_ADC | KI | Bezugsspannung für ADC | ||

| 68 | AVSS_2V5_ADC | P | Masse/Erde für ADC | ||

| 69 | EXT_PMU_EN | DO | Externe Stromversorgung, Ausgang aktivieren | ||

| 70 | WAKEUP | DI | Externe Reaktivierung aus dem tiefsten Energiesparmodus | Derzeit nicht unterstützt | |

| 71 | AVDD_3V3_RTC | PI | 3,3 V-Stromversorgungsschiene für Echtzeituhr | ||

| 72 | RTC_XIN | KI | Echtzeituhr-Quarzoszillatoreingang | ||

| 73 | RTC_XOUT | AO | Echtzeituhr-Quarzoszillatorausgang | ||

| 74 | AVDD_3V3_XPPLL | PI | 3,3 V-Stromversorgungsschiene für interne Phasenregelschleife (PLL) | ||

| 75 | I2S_MCLK0_ALT | AO | Analoge Alternative zu MCLK0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. | |

| 76 | I2S_MCLK1_ALT | AO | Analoge Alternative zu MCLK1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. | |

| 77 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 78 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 79 | VOUT_2V5 | PO | Ausgabe von internem 2,5 V-LDO | ||

| 80 | AVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 81 | PMU_EN | DI | Überschreiben der internen PMU | ||

| 82 | RESERVIERT | ||||

| 83 | GND | P | Masse/Erde | ||

| 84 | SENSE_1V15 | KI | Eingang erfassen, um die 1,15 V-Stromversorgung zu stabilisieren | ||

| 85 | VOUT_1V15 | PO | Ausgabe von internem 1,15 V-LDO | ||

| 86 | AVDD_1V6_CLDO | PI | 1,6 V-Stromversorgungsschiene für interne 1,15 V-Kern-LDO | ||

| 87 | PMU_CAP | A | Schließen Sie einen Kondensator zwischen diesem Pin und AVDD_3V3_BUCK an, um die Stabilität der PMU zu erhalten. | ||

| 88 | AVDD_3V3_BUCK | PI | 3,3 V-Stromversorgungsschiene für internen 1,6 V-Abwärts-Gleichstromwandler | ||

| 89 | AVDD_3V3_BUCK | PI | 3,3 V-Stromversorgungsschiene für internen 1,6 V-Abwärts-Gleichstromwandler | ||

| 90 | VOUT_1V6 | PO | Ausgang von internem 1,6 V-Abwärtswandler | ||

| 91 | VOUT_1V6 | PO | Ausgang von internem 1,6 V-Abwärtswandler | ||

| 92 | AVSS_3V3_BUCK | P | Masse/Erde für internen 1,6 V-Abwärtswandler | ||

| 93 | AVSS_3V3_BUCK | P | Masse/Erde für internen 1,6 V-Abwärtswandler | ||

| 94 | DEBUG_RXD | DI | Reserviert für Azure Sphere-Debuggen | ||

| 95 | DEBUG_TXD | DO | Reserviert für Azure Sphere-Debuggen | ||

| 96 | DEBUG_RTS | DO | Reserviert für Azure Sphere-Debuggen | ||

| 97 | DEBUG_CTS | DI | Reserviert für Azure Sphere-Debuggen | ||

| 98 | SWD_DIO | DIO | ARM SWD für Cortex-M4F-Debuggen | ||

| 99 | SWD_CLK | DI | ARM SWD für Cortex-M4F-Debuggen | ||

| 100 | SWO | DO | ARM SWO für Cortex-M4F-Debuggen | Derzeit nicht unterstützt | |

| 101 | GPIO56 | GPIO56/TX0 | DIO | GPIO mit Multiplexing für I2S 0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 102 | GPIO57 | GPIO57 /MCLK0 | DIO | GPIO mit Multiplexing für I2S 0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 103 | GPIO58 | GPIO58/FS0 | DIO | GPIO mit Multiplexing für I2S 0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 104 | GPIO59 | GPIO59/RX0 | DIO | GPIO mit Multiplexing für I2S 0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 105 | GPIO60 | GPIO60/BCLK0 | DIO | GPIO mit Multiplexing für I2S 0 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 106 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 107 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 108 | GPIO61 | GPIO61/TX1 | DIO | GPIO mit Multiplexing für I2S 1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 109 | GPIO62 | GPIO62/MCLK1 | DIO | GPIO mit Multiplexing für I2S 1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 110 | GPIO63 | GPIO63/FS1 | DIO | GPIO mit Multiplexing für I2S 1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 111 | GPIO64 | GPIO64/RX1 | DIO | GPIO mit Multiplexing für I2S 1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 112 | GPIO65 | GPIO65/BCLK1 | DIO | GPIO mit Multiplexing für I2S 1 | I2S wird derzeit nur für M4-Anwendungen unterstützt. |

| 113 | GPIO66 | GPIO66/SCLK3/TXD3 | DIO | GPIO mit Multiplexing für ISU 3-Funktionen | |

| 114 | GPIO67 | GPIO67/MOSI3/RTS3/SCL3 | DIO | GPIO mit Multiplexing für ISU 3-Funktionen | |

| 115 | GPIO68 | GPIO68/MISO3/RXD3/SDA3 | DIO | GPIO mit Multiplexing für ISU 3-Funktionen | |

| 116 | GPIO69 | GPIO69/CSA3/CTS3 | DIO | GPIO mit Multiplexing für ISU 3-Funktionen | |

| 117 | GPIO70 | GPIO70/CSB3 | DIO | GPIO mit Multiplexing für ISU 3-Funktionen | Unterstützt derzeit nur GPIO. |

| 118 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 119 | GPIO71 | GPIO71/SCLK4/TXD4 | DIO | GPIO mit Multiplexing für ISU 4-Funktionen | |

| 120 | GPIO72 | GPIO72/MOSI4/RTS4/SCL4 | DIO | GPIO mit Multiplexing für ISU 4-Funktionen | |

| 121 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 122 | GPIO73 | GPIO73/MISO4/RXD4/SDA4 | DIO | GPIO mit Multiplexing für ISU 4-Funktionen | |

| 123 | GPIO74 | GPIO74/CSA4/CTS4 | DIO | GPIO mit Multiplexing für ISU 4-Funktionen | |

| 124 | GPIO75 | GPIO75/CSB4 | DIO | GPIO mit Multiplexing für ISU 4-Funktionen | |

| 125 | SYSRST_N | DI | Systemzurücksetzung, aktiv niedrig | ||

| 126 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 127 | SERVICE_TXD | DO | Azure Sphere-Serviceport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 128 | SERVICE_RTS | DO | Azure Sphere-Serviceport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 129 | SERVICE_RXD | DI | Azure Sphere-Serviceport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 130 | SERVICE_CTS | DI | Azure Sphere-Serviceport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 131 | RESERVIERT | ||||

| 132 | DVDD_1V15 | PI | 1,15 V-Stromversorgungsschiene | ||

| 133 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 134 | RECOVERY_RXD | DI | Azure Sphere-Wiederherstellungsport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 135 | RECOVERY_TXD | DO | Azure Sphere-Wiederherstellungsport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 136 | RECOVERY_RTS | DO | Azure Sphere-Wiederherstellungsport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 137 | RECOVERY_CTS | DI | Azure Sphere-Wiederherstellungsport | Nicht verfügbar für die Verwendung durch Kundenanwendung. | |

| 138 | IO0_GPIO85 | IO0_GPIO85/IO0_RXD | DI | Dediziertes GPIO-Multiplexed mit UART für E/A M4 0 | |

| 139 | IO0_GPIO86 | IO0_GPIO86/IO0_TXD | DO | Dediziertes GPIO-Multiplexed mit UART für E/A M4 0 | |

| 140 | IO0_GPIO87 | IO0_GPIO87/IO0_RTS | DO | Dediziertes GPIO-Multiplexed mit UART für E/A M4 0 | |

| 141 | IO0_GPIO88 | IO0_GPIO88/IO0_CTS | DI | Dediziertes GPIO-Multiplexed mit UART für E/A M4 0 | |

| 142 | IO1_GPIO89 | IO1_GPIO89/IO1_RXD | DI | Dediziertes GPIO-Multiplexed mit UART für E/A M4 1 | |

| 143 | IO1_GPIO90 | IO1_GPIO90/IO1_TXD | DO | Dediziertes GPIO-Multiplexed mit UART für E/A M4 1 | |

| 144 | DVDD_3V3 | PI | 3,3 V-Stromversorgungsschiene | ||

| 145 | IO1_GPIO91 | IO1_GPIO91/IO1_RTS | DO | Dediziertes GPIO-Multiplexed mit UART für E/A M4 1 | |

| 146 | IO1_GPIO92 | IO1_GPIO92/IO1_CTS | DI | Dediziertes GPIO-Multiplexed mit UART für E/A M4 1 | |

| 147 | RESERVIERT | ||||

| 148 | TEST | DI | Muss für normalen Betrieb niedrig geregelt werden. | ||

| 149 | WF_G_RF_AUXIN | RF | 2,4 GHz-WLAN-Empfangs-Diversity-Port | ||

| 150 | NC | ||||

| 151 | AVDD_3V3_WF_G_PA | PI | 3,3 V-Stromversorgungsschiene für 2,4 GHz-WLAN-Leistungsverstärker | ||

| 152 | NC | ||||

| 153 | WF_G_RF_ION | RF | 2,4 GHz-WLAN-Antennenport (differenziell) | ||

| 154 | WF_G_RF_ION | RF | 2,4 GHz-WLAN-Antennenport (differenziell) | ||

| 155 | WF_G_RF_IOP | RF | 2,4 GHz-WLAN-Antennenport (differenziell) | ||

| 156 | WF_G_RF_IOP | RF | 2,4 GHz-WLAN-Antennenport (differenziell) | ||

| 157 | NC | ||||

| 158 | AVDD_3V3_WF_G_TX | PI | 3,3 V-Stromversorgungsschiene für 2,4 GHz-WLAN-Leistungsübertragung | ||

| 159 | WF_A_RF_AUXIN | RF | 5 GHz-WLAN-Empfangs-Diversity-Port | ||

| 160 | AVDD_3V3_WF_A_TX | PI | 3,3 V-Stromversorgungsschiene für 5 GHz-WLAN-Leistungsübertragung | ||

| 161 | NC | ||||

| 162 | WF_A_RFIO | RF | 5 GHz-WLAN-Antennenport (unsymmetrisch) | ||

| 163 | WF_A_RFIO | RF | 5 GHz-WLAN-Antennenport (unsymmetrisch) | ||

| 164 | GND | P | Masse/Erde | ||

| 165 | EPAD | P | Masse/Erde |